#### **GENERAL DESCRIPTION**

PJ11027 is a simple and efficient integrated synchronous buck converter. It features a wide input voltage range of 4.5V to 18V, making it well-suited for various common input voltage rails such as 12V and 15V. It supports a continuous output current of up to 2A, with an output voltage range from 0.768V to 7V.

PJ11027 works in pulse frequency modulation (PFM) mode to maintain high efficiency under light loads; PJ11027F operates in forced pulse-width modulation (FPWM) mode to achieve a fixed switching frequency and low output ripple under full load current.

PJ11027 integrated comprehensive protection features, including input under-voltage protection (UVLO), per-cycle valley current limit protection (OCL), output under-voltage protection (UVP), output overvoltage protection (OVP), and over-temperature protection (OTP), to ensure its safe and reliable operation under various working conditions.

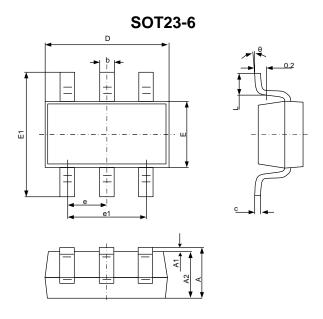

PJ11027 assemble in a compact SOT23-6 package and operates within a temperature range of -40°C to 125°C.

#### **FEATURES**

- ♦ Wide Operating Input Range: 4.5V to 18V

- Output Voltage Range: 0.768V to 7V

- **♦** Continuous Output Current: 2A

- ♦ Constant Switching Frequency: 600kHz

- 135mΩ / 70mΩ Low  $R_{DS(ON)}$  Power MOSFETs

- ◆ Low quiescent current (I<sub>Q</sub>): 190uA (Typ.)

- ♦ Low shutdown current (I<sub>SD</sub>): 2.5uA

- **♦** Fast load transient response by COT

- **♦** Optional Operation Modes Condition :

- PJ11027 : Pulse Frequency Modulation (PFM)

- PJ11027F : Forced Pulse Width Modulation (FPWM)

- ♦ High Reference Voltage Accuracy : 0.768V ±1.5%

- **♦** Complete Protections Integrated for Reliability:

- Internal 1ms Soft-Start Avoiding Inrush Current

- Cycle-by-Cycle Over Current Limit (OCL) :Peak Current Limit and Valley Current Limit

- Unlatched VIN UVLO, OVP, UVP, OVP and OTP

Protection

- ♦ Small Solution Size:

- SOT23-6 Package

#### **APPLICATIONS**

- ◆ Digital Set-Top Box and Surveillance

- ◆ TV / Monitor

- **♦** EPOS

- ♦ Home Networking Device and Wireless Router

- **♦** Smart Speaker

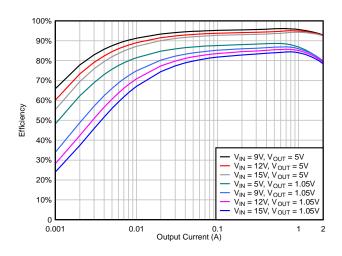

### **TYPICAL EFFICIENCY CURVE**

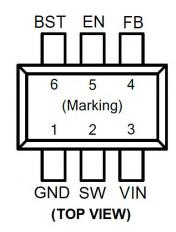

### **PIN CONFIGURATION**

### **ORDERING INFORMATION**

| ORDER NUMBER  | MODE | Marking ID | Package | Description                        |

|---------------|------|------------|---------|------------------------------------|

| PJ11027S6_R1  | PFM  | A6 DNN     | SOT23-6 | Halogen Free in T&R, 3000 pcs/Reel |

| PJ11027FS6_R1 | FPWM | A1 DNN     | SOT23-6 | Halogen Free in T&R, 3000 pcs/Reel |

### **FUNCTIONAL PIN DESCRIPTION**

| TERM   | MINAL | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                        |  |

|--------|-------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NUMBER | NAME  | 1,0                |                                                                                                                                                                    |  |

| 1      | GND   | G                  | Power Ground and Signal Ground.                                                                                                                                    |  |

| 2      | SW    | Р                  | Switch Node. Connect to power inductor with short and wide trace.                                                                                                  |  |

| 3      | VIN   | Р                  | Input Power Supply. Add a 100nF ceramic decoupling capacitor as close to VIN and GND pins as possible.                                                             |  |

| 4      | FB    | I                  | <b>Feedback Input</b> . Sense output voltage through the resistor divider for setting and controlling the output voltage.                                          |  |

| 5      | EN    | ı                  | Enable Control Pin. Drive EN pin high to enable the device or low to disable the device.                                                                           |  |

| 6      | BST   | Р                  | <b>Bootstrap Pin.</b> A capacitor rating 100nF must be connect from this pin to LX. It can be boost the gate drive to fully turn on the internal high side MOSFET. |  |

<sup>(1)</sup> I – Input; O – Output; P – Power; G – Ground

### **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature range (unless otherwise noted) (1)

|                                           | PARAMETER                            | MIN  | MAX | Unit |

|-------------------------------------------|--------------------------------------|------|-----|------|

|                                           | VIN, SW                              | -0.3 | 19  | V    |

|                                           | SW, Transient <10 ns                 | -3   | 21  | V    |

|                                           | VIN – SW,                            | -0.3 | 19  | V    |

| Voltage range at terminals <sup>(2)</sup> | VIN – SW, Transient < 10 ns          | -3   | 21  | V    |

|                                           | BST                                  | -0.3 | 25  | V    |

|                                           | BST – SW                             | -0.3 | 6   | V    |

|                                           | EN, FB                               | -0.3 | 6   | V    |

| T <sub>J</sub> (2)                        | Operating junction temperature range | -40  | 150 | °C   |

| T <sub>STG</sub>                          | Storage temperature range            | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### HANDLING RATINGS

| PARAMETER          | DEFINITION                                                 | MIN  | MAX | UNIT |

|--------------------|------------------------------------------------------------|------|-----|------|

| F0D(1)             | Human Body Model (HBM) ESD stress voltage <sup>(2)</sup>   |      | 2   | kV   |

| ESD <sup>(1)</sup> | Charged Device Model (CDM) ESD stress voltage(3), all pins | -500 | 500 | V    |

<sup>(1)</sup> Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges into the device.

#### RECOMMENDED OPERATING CONDITIONS

|                  | PARAMETER                      |       |     | MAX | UNIT |

|------------------|--------------------------------|-------|-----|-----|------|

| V <sub>IN</sub>  | Input voltage range            | 4.5   |     | 18  | V    |

| V <sub>OUT</sub> | Output voltage range           | 0.768 |     | 7   | V    |

| Fsw              | Buck switching frequency range |       | 600 |     | kHz  |

| l <sub>оит</sub> | Output DC current range        | 0     |     | 2   | Α    |

| TJ               | Operating junction temperature | -40   |     | 125 | °C   |

<sup>(2)</sup> Operating at junction temperatures greater than 125°C, although possible, degrades the lifetime of the device.

<sup>(2)</sup> Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(3)</sup> Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### THERMAL INFORMATION

|                                     | THERMAL RESISTANCE                                    | SOT23-6 | UNIT |

|-------------------------------------|-------------------------------------------------------|---------|------|

| Θ <sub>JA</sub> <sup>(2)</sup>      | Junction to ambient thermal resistance (JESD 51-7)    | 130.6   | °C/W |

| ОЈВ                                 | Junction to PCB thermal resistance                    | 84.6    | °C/W |

| ОЈС                                 | Junction to case thermal resistance                   | 28.4    | °C/W |

| Θ <sub>JA(EVM)</sub> <sup>(1)</sup> | Junction to ambient thermal resistance (Specific EVM) | 69      | °C/W |

<sup>(1)</sup> R<sub>θJA(EVM)</sub> is based on the thermal resistance information measured during the actual operation of the corresponding evaluation Module. EVM information: 60mm x 45mm, FR-4, TG150, 1.6mm thickness, 2-layer 2-Oz Cu copper. Operating Condition: V<sub>IN</sub> = 12V, V<sub>OUT</sub> = 5V, I<sub>OUT</sub> = 2A, T<sub>A</sub> = 25°C. This thermal resistance information is for reference only. The actual thermal resistance depends on PCB board layout, and test environment conditions.

### **ELECTRICAL CHARACTERISTICS**

$T_J$  = -40°C to 125°C,  $V_{IN}$  = 12V. Typical value is tested at  $T_J$  = +25°C, unless otherwise noted.

| PARAMETER            |                                              | TEST CONDITIONS                                                                                   | MIN   | TYP   | MAX   | UNIT |

|----------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| SUPPLY V             | OLTAGE                                       |                                                                                                   |       |       |       |      |

| V <sub>IN</sub>      | Input voltage range                          |                                                                                                   | 4.5   |       | 18    | V    |

| V                    | Under voltage lockout threshold              | V <sub>IN</sub> rising                                                                            | 4.0   | 4.2   | 4.4   | V    |

| $V_{IN\_UVLO}$       | Orider voltage lockout threshold             | V <sub>IN</sub> falling                                                                           | 3.6   | 3.8   | 4.0   | V    |

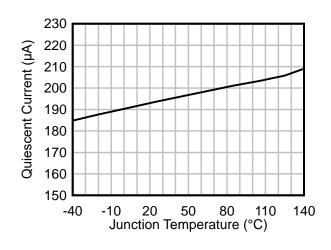

| l                    | Quiescent current into the VIN pin, PJ11027  | Non-switching, $V_{EN} = 5 \text{ V}$ , $V_{FB} = V_{REF} \times 105\%$ , $I_{OUT} = 0 \text{ A}$ |       | 190   | 220   | μΑ   |

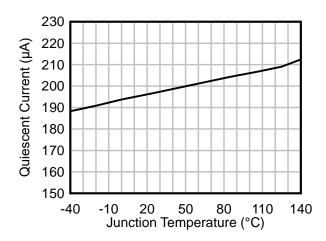

| I <sub>Q(VIN)</sub>  | Quiescent current into the VIN pin, PJ11027F | Non-switching, $V_{EN} = 5 \text{ V}$ , $V_{FB} = V_{REF} \times 105\%$ , $I_{OUT} = 0 \text{ A}$ |       | 193   | 220   | μА   |

| I <sub>SD(VIN)</sub> | Shutdown current into the VIN pin            | IC disabled, V <sub>IN</sub> = 12V, V <sub>EN</sub> = 0V                                          |       | 2.5   | 4.5   | μA   |

| EN                   |                                              |                                                                                                   |       |       |       |      |

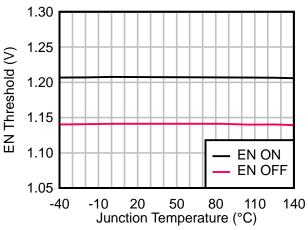

| $V_{\text{EN(R)}}$   | EN input level to start switching            | Rising threshold                                                                                  | 1.15  | 1.21  | 1.27  | V    |

| $V_{\text{EN(F)}}$   | EN input level to stop switching             | Falling threshold                                                                                 | 1.08  | 1.14  | 1.20  | V    |

| I <sub>EN(P)</sub>   | EN input current                             | V <sub>EN</sub> = 1.0V                                                                            | 0.84  | 1.11  | 1.38  | uA   |

| I <sub>EN(H)</sub>   | EN hysteresis current                        |                                                                                                   | 2.27  | 2.72  | 3.23  | uA   |

| FB                   |                                              |                                                                                                   |       |       |       |      |

| .,                   | ED Voltage                                   | T <sub>J</sub> = 25 ℃                                                                             | 0.756 | 0.768 | 0.780 | V    |

| $V_{FB}$             | FB Voltage                                   | T <sub>J</sub> = -40 °C to 125 °C, V <sub>IN</sub> = 12V                                          | 0.753 | 0.768 | 0.783 | V    |

| I <sub>FB(LKG)</sub> | FB Input Leakage Current                     | T <sub>J</sub> = 25 °C                                                                            | -100  | 0     | 100   | nA   |

<sup>(2)</sup> Measured on JESD51-7, 4-layer PCB.

|                                    | PARAMETER                                    | TEST CONDITIONS                                      | MIN  | TYP  | MAX  | UNIT |

|------------------------------------|----------------------------------------------|------------------------------------------------------|------|------|------|------|

| STARUP                             |                                              |                                                      | _    |      |      |      |

| T <sub>SS</sub>                    | Internal Fixed Soft-start Time               | 10% V <sub>OUT</sub> to 90% V <sub>OUT</sub>         | 0.5  | 1    | 1.5  | mS   |

| T <sub>DLY</sub>                   | EN Delay Time                                | EN High to 1 <sup>st</sup> Switching Pulse           |      | 400  |      | uS   |

| SWITCHING                          | G FREQUENCY                                  |                                                      | 1    |      |      |      |

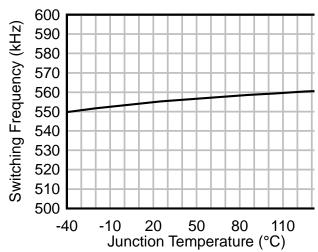

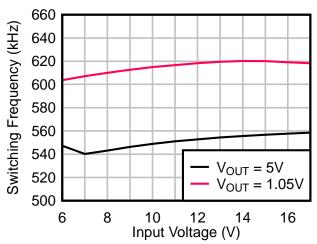

| F <sub>SW</sub>                    | Switching Frequency, CCM Mode                | V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.05V, CCM |      | 600  |      | kHz  |

| POWER ST                           | TAGE .                                       |                                                      |      |      |      |      |

| R <sub>DSON(HS)</sub>              | High-Side MOSFET<br>On-Resistance            | $T_J = 25$ °C, $V_{IN} = 12V$ , $V_{BOOT-SW} = 5V$   |      | 135  |      | mΩ   |

| R <sub>DSON(LS)</sub>              | Low-Side MOSFET<br>On-Resistance             | $T_J = 25$ °C, $V_{IN} = 12V$ , $V_{BOOT-SW} = 5V$   |      | 70   |      | mΩ   |

| T <sub>ON_MIN</sub> <sup>(1)</sup> | Minimum On Pulse Width                       |                                                      |      | 50   |      | nS   |

| T <sub>OFF_MIN</sub>               | Minimum Off Pulse Width                      |                                                      |      | 200  |      | nS   |

| $T_{DEAD}$                         | Dead Time                                    |                                                      |      | 10   |      | nS   |

| I <sub>ZC</sub>                    | Zero-cross detection current                 |                                                      |      | 80   |      | mA   |

| D <sub>MAX</sub>                   | Maximum Duty                                 |                                                      |      | 75   |      | %    |

| OVER CUR                           | RENT PROTECTION                              |                                                      | 1    |      |      | 1    |

| I <sub>LS(OC)</sub>                | Low-side Valley Current Limit                | V <sub>IN</sub> = 12V                                | 2.7  | 3.1  | 3.5  | Α    |

| I <sub>LS(NOC)</sub>               | Low-side Negative Current Limit,<br>PJ11027F | V <sub>IN</sub> = 12V                                | 0.85 | 1.15 | 1.45 | А    |

| OUTPUT O                           | VP AND UVP                                   |                                                      |      |      |      | •    |

| $V_{\text{OVP\_HYS}}$              | OVP Hysteresis                               |                                                      |      | 6.5  |      | %    |

| $V_{\text{OVP\_R}}$                | OVP Rising                                   |                                                      |      | 115  |      | %    |

| $V_{UVP\_F}$                       | UVP Failing                                  |                                                      |      | 65   |      | %    |

| V <sub>UVP_HYS</sub>               | UVP Hysteresis                               |                                                      |      | 6.5  |      | %    |

| T <sub>HCP(WAIT)</sub>             | Wait Time before Entering UV<br>Hiccup       |                                                      |      | 110  |      | uS   |

| T <sub>HCP(OFF)</sub>              | UVP Hiccup Time before<br>Re-startup         |                                                      | 12   |      |      | mS   |

| OVER TEM                           | IPERATURE PROTECTION                         |                                                      |      |      |      |      |

| _                                  | Thermal shutdown temperature                 |                                                      |      | 150  |      | °C   |

| T <sub>SD</sub>                    | Thermal shutdown hysteresis                  |                                                      |      | 30   |      | °C   |

|                                    | 1                                            |                                                      |      |      |      |      |

<sup>(1)</sup> Guaranteed by design

### **Typical Operating Characteristics**

Test Conditions: V<sub>IN</sub> = 12V, T<sub>A</sub> = 25°C (unless otherwise noted)

Figure-1. Quiescent Current (PJ11027) VS. Temp.

Figure-2. Quiescent Current (PJ11027F) VS. Temp.

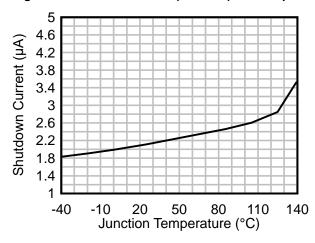

Figure-3. Shutdown Current VS. Temp.

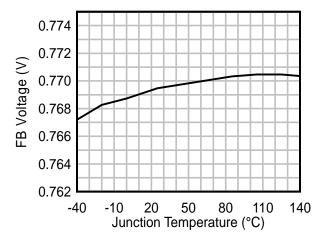

Figure-4. Reference Voltage VS. Temp.

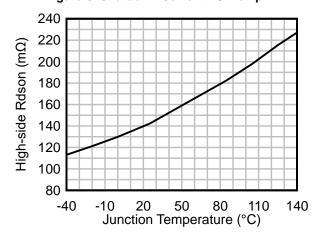

Figure-5. High-Side R<sub>DS(ON)</sub> VS. Temp.

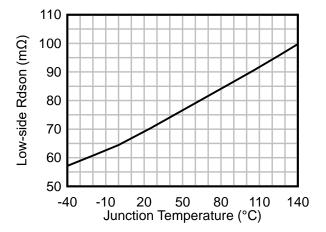

Figure-6. Low-Side R<sub>DS(ON)</sub> VS. Temp.

Test Conditions: V<sub>IN</sub> = 12V, T<sub>A</sub> = 25°C (unless otherwise noted)

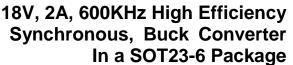

Figure-7. UVLO Threshold VS. Temp.

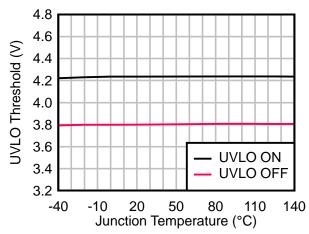

Figure-9. Valley Current Limit VS. Temp.

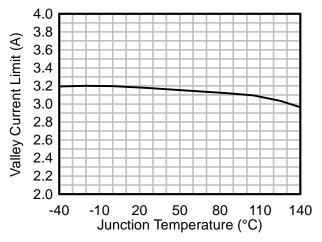

Figure-11. Switching Frequency (PJ11027) VS. IOUT

Figure-8. EN Pin Threshold VS. Temp.

Figure-10. Switching Frequency VS. Temp.

Figure-12. Switching Frequency (PJ11027F) VS. VIN

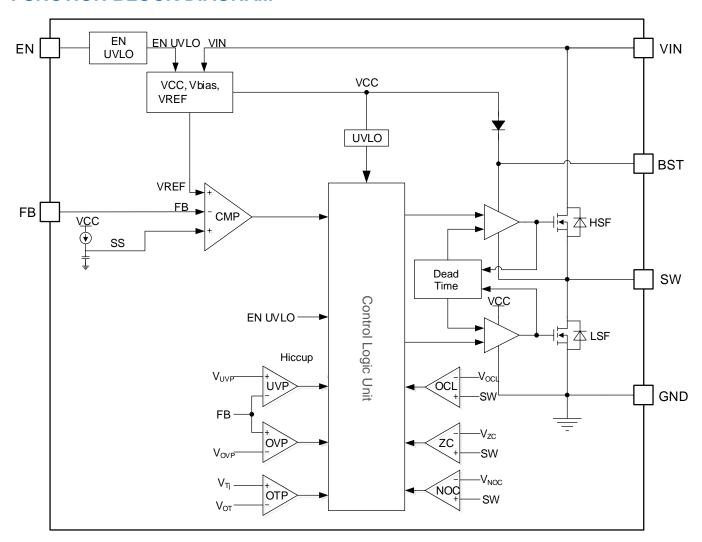

### **FUNCTION BLOCK DIAGRAM**

### **FEATURE DESCRIPTION**

#### Overview

PJ11027 is a wide range of medium voltage input 4.5V-18V with 2A DC synchronous buck converter, especially for input voltage rails of 12V. Constant-on-time (COT) control is employed to provide fast transient response and easy loop stabilization, this helps designer save capacitance and reduces the cost of overall size. The internal on-time timer of PJ11027 is inversely proportional to the input voltage and directly proportional to the output voltage, allowing for a consistent operating frequency under various working conditions. Also integrates an additional output voltage error amplifier,

capable of eliminating the DC output voltage offset caused by the half ripple of the COT control. This results got the higher output voltage accuracy and load regulation. During the light-load conditions, PJ11027 operates in Pulse Frequency Modulation (PFM) mode, maintaining high light-load output efficiency by reducing the switching frequency. On the other hand, PJ11027F operates in Forced Pulse Width Modulation (FPWM) mode, keeping a constant switching frequency to minimize output voltage ripple.

### **Device Operation Modes**

#### **Constant On-Time Control**

PJ11027 employs Constant On-Time Control (COT) with a built-in voltage error integrator. COT control utilizes the output voltage valley ripple based on a comparator and on-time timer to achieve output voltage regulation.

At the beginning of each cycle, whenever the voltage on the feedback pin (FB) drops below the internal reference voltage, the internal high-side MOSFET (HS-FET) is turned on, it remains on for a fixed on-time duration before being turned off, and the on-time timer determines this on-time duration. The on-time timer is determined by both the output voltage and the input voltage to keep the switching frequency near constant over the full input voltage range. When the on-time timer has timed out, the HS-FET will remain off for at least 200ns (minimum turn-off time). After it, if the voltage on the feedback pin FB is lower than the internal reference voltage. the HSF will turn on again for a fixed on-time. By doing this, the converter achieves a quasi-constant frequency while maintaining a stable output voltage.

PJ11027 integrated a ripple injection circuit to simulate the output voltage ripple to achieve stable operation under low output ripple conditions with a low ESR ceramic output capacitor (MLCC). In addition, a ramp signal generation circuit is integrated to minimize switching jitter.

# Pulse Frequency Modulation and Forced Pulse Width Modulation (FPWM)

PJ11027 automatically works in Pulse Frequency Modulation (PFM) mode under light load operation to maintain high efficiency at light loads. As the load current decreases, the valley of the inductor current ripple decreases until the inductor current valley drops to zero amps, which is the critical point between the continuous and discontinuous inductor current conduction modes - the inductor current critical conduction mode. Continuing to reduce the load current, PJ11027 will turn off the low-side

MOSFET (LS-FET) when it detects that the inductor current has passed zero, thus keeping the inductor current at zero. In this case, the output capacitor is only discharged by the load current and the output voltage drops slower, thus the switching frequency will be reduced. As the switching frequency is reduced, the switching loss at light- load will also be reduced, which improves the light- load efficiency of the system.

PJ11027F works in forced pulse width modulation mode (FPWM) under light-load conditions to keep the switching frequency constant and maintain low output voltage ripple. When the HS-FET is off, the LS-FET is forced open after a dead time of 10ns until it closes before the HS-FET opens on the next cycle. This mode of operation does not detect the inductor current crossing point and allows the inductor current to flow through the drain-source terminal of the LS-FET from the output capacitor to the switching node, known as reverse current. In this case, the switching frequency remains nearly constant over the entire load current range, achieving low light-load output voltage ripple.

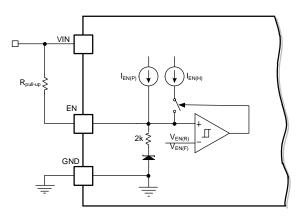

#### **Precise Enable Control and UVLO**

PJ11027 provides a chip external enable control pin (EN) to enable or disable chip operation. The chip is enabled for normal operation when the EN pin voltage exceeds the EN rising threshold voltage ( $V_{EN(R)}$ ) and the  $V_{IN}$  voltage exceeds the  $V_{IN}$  under-voltage lockout threshold ( $V_{UVLO(R)}$ ). If the EN pin voltage is pulled down below the threshold voltage ( $V_{EN(F)}$ ), the chip stops switching and enters the shutdown mode, even if the VIN voltage is higher than the VIN under-voltage lockout threshold ( $V_{UVLO(R)}$ ), the chip is disabled and the switching action stops. In shutdown mode, the chip's input current is reduced to the lowest shutdown current (2.5µA typical).

The EN pin has an internal pull-up current that allows the user to leave the EN pin open to enable the chip. Alternatively, depending on the application, the EN pin can be connected to an external logic controller to enable control of the chip. A 5V Zener diode (typical breakdown voltage 6.9V) is integrated into the EN pin to protect the internal circuits from over-voltage risk.

When externalizing the EN pin to voltages higher than 6V, such as VIN, a pull-up resistor (not less than  $100k\Omega$ ) is added in series to limit the input current to the EN pin and prevent damage to the Zener diode, as shown in Figure below.

Figure-13. Pull-up Resistor to VIN

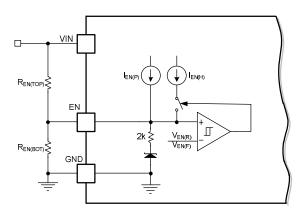

The  $V_{IN}$  under-voltage lockout (UVLO) function prohibits the chip from operating when the input supply voltage is too low. The UVLO comparator monitors of the internal regulator, VCC. When  $V_{IN}$  drops below  $V_{UVLO(F)}$ , the chip stops switching and disables enable. When VIN rises up  $V_{UVLO(R)}$ , if  $V_{EN}$  is also greater than  $V_{EN(R)}$  at that time, the chip will be enabled to start soft-start to resume normal operation.

Figure-14. V<sub>IN</sub> UVLO BLOCK

The  $V_{\text{IN}}$  UVLO rise and fall thresholds of the PJ11027 are fixed and the typical hysteresis voltage is 400 mV. If higher thresholds and hysteresis voltages are required in practical applications, the chip supports the customization of the  $V_{\text{IN}}$  UVLO rise and  $V_{\text{IN}}$  UVLO fall thresholds by connecting a voltage divider

resistor to the EN pin to avoid repeated reboots of the chip due to the spike noise and ripples of the  $V_{IN}$  at the switch-on time. This prevents the chip from restarting repeatedly due to  $V_{IN}$  spike noise and ripple at the switch-on time, as shown in Figure-14.

The EN pin has an internal pull-up current ( $I_{EN(P)}$ ) that enables the chip when the EN pin is externally suspended. The pull-up current can also be used to set the voltage threshold and hysteresis for the external  $V_{IN}$  UVLO function. The EN pin voltage,  $V_{EN}$ , is divided by  $V_{IN}$ , and as  $V_{EN}$  rises with  $V_{IN}$  and becomes greater than  $V_{EN(R)}$ , an additional pull-up hysteresis current ( $I_{EN(H)}$ ) is turned on to change the ratio of the  $V_{EN}$  voltages, allowing for customized configurations of rising and falling thresholds. The  $R_{EN(TOP)}$  and  $R_{EN(BOT)}$  configurations for the specified  $V_{IN}$  UVLO thresholds can be calculated using Equation-1 and Equation-2 below, where  $V_{IN(START)}$  and  $V_{IN(STOP)}$  are the custom configured input startup and shutdown voltage values.

$$R_{\text{EN(TOP)}} = \frac{V_{\text{IN(START)}}}{I_{\text{EN(P)}}} \frac{V_{\text{EN(F)}}}{V_{\text{EN(R)}}} - V_{\text{IN(STOP)}}}{I_{\text{EN(P)}} \left(1 - \frac{V_{\text{EN(F)}}}{V_{\text{EN(R)}}}\right) + I_{\text{EN(H)}}}$$

Equation-1

$$R_{\text{en(BOT)}} \, = \, \frac{R_{\text{en(TOP)}} V_{\text{en(F)}}}{V_{\text{In(STOP)}} \, - \, V_{\text{en(F)}} \, + \, R_{\text{en(TOP)}} (I_{\text{en(P)}} \, + \, I_{\text{en(H)}})}$$

**Equation-2**

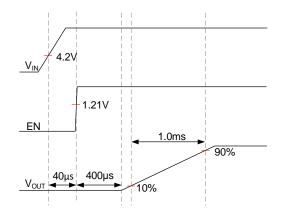

#### Soft Start and Pre-biased Soft Start

PJ11027 integrated an internal soft-start function to minimize the inrush current and ensure a smooth rise of the output voltage during the chip startup power-up process. When  $V_{IN}$  exceeds the UVLO threshold, the output voltage starts to rise after a delay of 440µs (typical) from the rising edge of EN. When the chip starts up, the internal soft-start circuitry generates a soft-start voltage (SS) that rises from zero. When SS is lower than the internal reference voltage ( $V_{REF}$ ), SS overrides  $V_{REF}$ , so the voltage error integrator and control comparator use SS as the reference voltage, and the output voltage rises smoothly following SS. When SS rises to the  $V_{REF}$  voltage,  $V_{REF}$  regains control, the reference voltage stabilizes to  $V_{REF}$ , and

the output voltage then stabilizes to the set value  $V_{\text{OUT}}$ , and the soft-start is completed. The internal soft-start time,  $T_{\text{SS}}$  is fixed at 1ms, and is specified to be the time for the output voltage to rise from 10% to 90%.

If the output capacitor is already in a pre-biased voltage state when the chip starts up, PJ11027 activates the switch only after the internal reference voltage SS is greater than the feedback voltage  $V_{FB}$  and  $V_{OUT}$  starts to rise. This pre-bias soft-start scheme ensures that the chip's output voltage rises smoothly into a steady state.

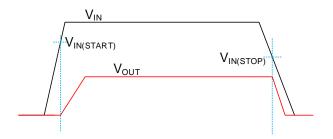

Figure-15. Start-up and Stop Voltage

Figure-16. Soft-Start Timing Diagram

#### **Output UVP with Hiccup mode**

PJ11027 integrated an output under-voltage hiccup protection (UVP) that prevents the chip's outputs from being overloaded or shorted by constantly monitoring the feedback voltage  $V_{FB}$ . If  $V_{FB}$  lower than the output under-voltage protection threshold ( $V_{UVP}$ ) (typically 65% of the internal feedback reference voltage), the output of the under-voltage comparator will be set high to shut down the internal

high/low-side MOSFET, preventing the chip from continuing switching operation.

If the output under-voltage condition lasts longer than the fixed wait time (Thcp(WAIT)), PJ11027 will enter output under-voltage protection (UVP) in hiccup mode. In hiccup mode, the chip will turn off the internal high-side and low-side MOSFET first for a fixed hiccup time (Thiccup(OFF)) and then attempt an automatic soft-start restart. After the soft-start is completed, if the fault condition is removed, the chip will resume normal operation; otherwise, it will continue to enter the hiccup protection and then automatic restart cycle until the fault condition is removed.

Figure-17. UVP Hiccup mode

Figure-18. UVP Hiccup recovery

### **Peak and Valley Over-Current Limit**

PJ11027 integrated valley current limit (OCL) protection. Whenever the internal low-side MOSFET on state, the chip detects the inductor current, and when the inductor current is greater than the current-limit threshold (I<sub>LS(OC)</sub>), the current-limit comparator flips and PJ11027 enters the OCL mode.

At this time, the internal high-side MOSFET remains off until the inductor current drops below the current limit threshold ( $I_{LS(OC)}$ ). If the load current of the chip exceeds the inductor current (inductor current is clamped by OCL), the output capacitor needs to supply additional current, thus the output capacitor discharges and the output voltage starts to drop. When the output voltage falls below the output under-voltage protection threshold ( $V_{UVP}$ ), the chip stops operating and enters the UVP hiccup mode to avoid high temperature rise.

#### **Negative Over-Current Limit (P11027F only)**

PJ11027F works in FPWM mode under light-load conditions, which allows the low side MOSFET to pass reverse current. In FPWM mode, if the output is accidentally connected to an external power supply, the chip may operate in reverse boost mode, generating high reverse current to damage the chip PJ11027F integrated low-side MOSFET current detection circuitry, which immediately turns off the low-side MOSFET when it detects that the low-side MOSFET reverse current is greater than the threshold of inverse current limitation (NOC), and then turns on the high-side MOSFET to drain the output inductor of energy. Then the high-side MOSFET is turned on to drain the energy from the output inductor. This function protects the low-side MOSFET by limiting the reverse current above the NOC threshold, and the NOC current limit does not take effect during the minimum turn-off time.

#### **Output Over-Voltage Protection**

PJ11027 integrated an output over voltage protection (OVP) function to minimize output voltage overshoot and to protect downstream power equipment from damage caused by high voltage spikes that may occur during output fault conditions or sudden load reductions. The OVP circuitry detects overvoltage conditions by monitoring the feedback voltage (VFB). When VFB exceeds the OVP threshold (VOVP), the OVP comparator output goes high and both the built-in high-side and low-side MOSFETs shut down to prevent VOUT from rising further. Once VOUT falls below VOVP, the chip starts working again. The output overvoltage protection function is non-latching.

#### **Over Temperature Protection**

PJ11027 is owned with an over temperature protection (OTP) function to prevent the chip from overheating due to excessive power dissipation. The internal circuitry of the chip detects the junction temperature of the chip, and when the junction temperature exceeds the over-temperature protection threshold ( $T_{J(SD)}$ ), the OTP comparator flips and the chip stops the switching action, thus the junction temperature decreases. Once the junction temperature drops below the over-temperature protection hysteresis threshold ( $T_{J(HYS)}$ ), the chip will resume normal operation and start soft start again.

#### APPLICATION INFORMATION

#### Overview

The output of the synchronous buck converter is mainly composed of inductors and capacitors, and the energy is stored and transferred to the load through the switching of the internally integrated power MOSFET, and a second-order low-pass filter is formed to smooth out the switching node voltage to obtain a stable output DC voltage. This section mainly describes the detailed design process based on the design example.

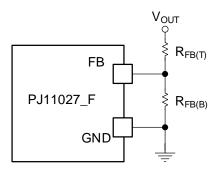

#### **Output Voltage Setting**

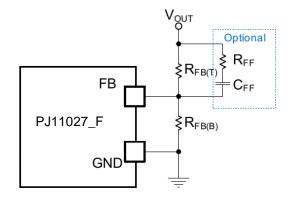

As shown in Figure-19., PJ11027 can be set to different output voltages by using an external divider resistor connected to the FB pin. The formula for the output voltage versus the external divider resistor is as follows:

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R_{FB(T)}}{R_{FB(B)}}\right)$$

Equation-3

Where VREF = 0.768V

Figure-19. Output voltage setting

It is recommended to start the design with the voltage divider resistor  $R_{FB(B)}.$  Larger  $R_{FB(B)}$  will cause the FB pin to be more susceptible to external noise interference, while too small RFB(B) will increase the power loss of the divider resistor. Considering both, it is recommended to choose  $R_{FB(B)}$  =  $10k\Omega{\sim}50k\Omega,$  and the voltage divider resistor  $R_{FB(T)}$  can be calculated with Equation:

$$R_{FB(T)} = R_{FB(B)} \times \left(\frac{V_{OUT}}{V_{REF}} - 1\right)$$

Equation-4

Where  $V_{REF} = 0.768V$

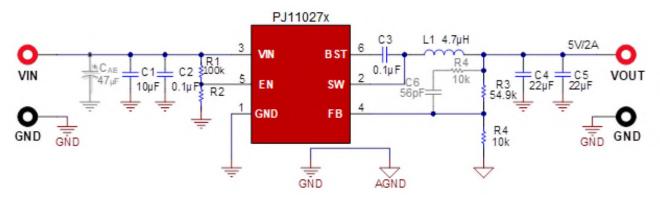

For example, an output voltage of 5V, take  $R_{FB(B)}$  to be  $10k\Omega$  and calculate  $R_{FB(T)}$  to be  $55.1k\Omega$ , and select a nominal chip resistor of  $54.9k\Omega$  accordingly. For applications requiring high output voltage accuracy, 1% or higher precision voltage divider resistors are recommended.

PJ11027 is designed to work in the range of 4.5V to 18V. The buck converter requires an input voltage higher than the output voltage and with a recommended maximum operating duty cycle of 75%, the recommended minimum input voltage is Vout/0.75. The chip does not allow the output voltage to be higher than the input voltage, which is discharged through the high-side power body diode to the input supply. The resulting reverse current may cause unpredictable behavior. If such an application condition occurs, a diode by series, for example, can be added to block this reverse current.

#### Input Startup and Shutdown Voltage Setting

As shown in Figure-15. V<sub>IN</sub> UVLO Threshold Setting and Figure-16. Input Startup Voltage and Shutdown Voltage Schematic, set the input startup voltage, V<sub>IN(START)</sub>, and the input shutdown voltage, V<sub>IN(STOP)</sub>, respectively, by configuring the EN divider resistor.

For example, 12V input voltage and 5V output voltage, the input startup voltage  $V_{\text{IN(START)}} = 8V$  and the input shutdown voltage  $V_{\text{IN(STOP)}} = 7V$  can be configured by selecting EN resistor.  $I_{\text{EN(P)}} = 1.11 \mu\text{A}$ ,

$I_{EN(H)}$  = 2.72μA into Equation-1 and Equation-2 to get  $R_{EN(TOP)}$  = 215k $\Omega$ ,  $R_{EN(BOT)}$  = 36.5k $\Omega$ . For applications where the EN pin is directly controlled by a digital signal GPIO port, a GPIO port can be directly connected to the EN pin. If the chip does not start up when the GPIO port is in a high resistance state, it is recommended to add a pull-down resistor of less than 500k $\Omega$  to the EN pin.

#### **Output Inductor Selection**

Inductor selection based on the size, cost, efficiency and transient response performance of the chip solution. Three key parameters are considered: Inductance (L), Inductor Saturation current (Isat) and inductor DC resistance (DCR). As a compromise between inductor size and power consumption, it is recommended that the inductor be selected so that the ripple of the inductor current ( $\Delta I_L$ ) is 20% to 50% of the rated current ( $I_{rated}$ ) of the PJ11027 as shown in the following equation:

$$L = \frac{V_{\text{out}} \times \left(V_{\text{IN}} - V_{\text{out}}\right)}{V_{\text{IN}} \times f_{\text{SW}} \times \Delta I_{\text{I}}} = \frac{V_{\text{out}} \times \left(V_{\text{IN}} - V_{\text{out}}\right)}{V_{\text{IN}} \times f_{\text{SW}} \times I_{\text{cand}} \times K_{\text{I}}}$$

**Equation-5**

where

VIN is input voltage,

V<sub>OUT</sub> is output voltage,

fsw is switching frequency,

Irated is the rated current of 2A

K<sub>L</sub> is the current ripple factor: 20%-50%

PJ11027 adopts COT control architecture and is optimized for common output voltages. It is recommended to refer to Table-1 directly for inductor selection. After selecting the inductance value according to Table-1, the actual inductor current ripple  $\Delta I_L$  and peak value ( $I_{L(peak)}$ ) can be calculated by the following equations:

$$\Delta I_{L} = \frac{V_{OUT} \times \left(V_{IN} - V_{OUT}\right)}{V_{IN} \times f_{SW} \times L}$$

Equation-6

$$I_{L(peak)} = I_{OUT(MAX)} + \frac{\Delta I_{L}}{2}$$

Equation-7

where

IOUT(MAX) is the maximum output current

Select an inductor with a saturation current value ISAT that is at least greater than the inductor peak current IL(peak), and leave enough margin (e.g. 10%) to ensure that the inductor will not saturate during normal steady-state operation of the chip.

Due to the chip in the power-on startup, output overcurrent or load jump conditions, the inductor current may temporarily rise to greater than the peak current value IL(peak) in steady-state operation, at this time, a more conservative choice is to select the saturation current value ISAT is greater than the chip current limit IL(max\_peak) inductor, to ensure that the inductor will not be saturated under any circumstances, check following equation.

$$I_{L(max\_peak)} = I_{LS(OC)} + \Delta I_L$$

Equation-8

Where

ILS(OC) is the valley current value of the chip

IL(max\_peak) is the peak inductor current of the chip with the current limited in case

Considering that the output voltage of this example is 5V, a  $4.7\mu H$  inductor is directly selected according to Table-1. Then the actual inductor ripple and peak current are:

$$\Delta I_{L} = \frac{5 \times (12 - 5)}{12 \times 580 \text{k} \times 4.7 \text{u}} = 1.07 \text{A}$$

$$I_{\text{L(peak)}} = \ 2 + \frac{1.07}{2} \ = \ 2.535 A$$

If a  $4.7\mu H$  inductor is selected, make sure that the saturation current and rated current of the selected inductor are at least 2.535A. In addition, the peak inductor current can be calculated to take into account the load overcurrent:

$$I_{1 \text{(max peak)}} = 3.1 + 1.07 = 4.17A$$

The most choice is to ensure that the saturation current of the selected inductor is greater than 4.17A.

#### **Output Capacitor Selection**

The selection of the output capacitor is related to the ripple of the output voltage and the voltage response performance when the load jumps. PJ11027 adopts the optimized COT control architecture after considering the actual application of ceramic capacitors, which achieves the ultra-fast load transient response and maintains the stable operation of the chip at the same time. In order to achieve the most suitable transient response performance, the recommended output capacitors and inductors are shown in Table-1:

$V_{RIPPLE}$  output voltage ripple consists of two parts. One is the resistive ripple  $V_{RIPPLE(ESR)}$  generated by the inductor current on the equivalent series resistance ESR of the output capacitor; the other one is the capacitive ripple  $V_{RIPPLE(C)}$  generated by the inductor ripple current charging and discharging the output capacitor. The calculation equation as follows:

$$V_{RIPPLE} = \sqrt{V_{RIPPLE(ESR)}^2 + V_{RIPPLE(C)}^2}$$

Equation-9

$$V_{\text{RIPPLE}(\text{ESR})} = \Delta I_{\text{L}} \times \text{ESR}$$

Equation-10

$$V_{RIPPLE(C)} = \frac{\Delta I_{L}}{8 \times C_{OUT} \times f_{ew}}$$

Equation-11

The actual ripple can simply be estimated as:

$$\begin{aligned} & V_{\text{RIPPLE}} \ > \ \text{Max} \Big( V_{\text{RIPPLE(ESR)}}, \ V_{\text{RIPPLE(C)}} \Big) \\ & V_{\text{RIPPLE}} \ < \ V_{\text{RIPPLE(ESR)}} \ + \ V_{\text{RIPPLE(C)}} \end{aligned}$$

Equation-12

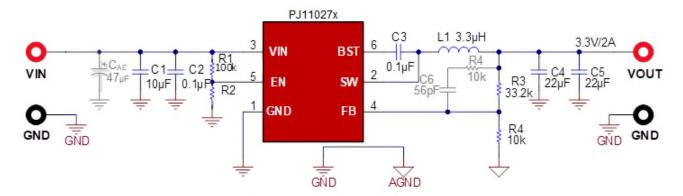

Considering this design example, two  $22\mu F/16V$  ceramic capacitors are selected as the output capacitors according to Table-1. With the output voltage  $V_{OUT}=5V$ , the actual total effective capacitance value is  $14\mu F$  ( $7\mu Fx2$ ) and the actual equivalent ESR is  $0.8m\Omega$  ( $1.6m\Omega/2$ ), the output ripple  $V_{RIPPLE}$  can be calculated as follows:

$$V_{\text{RIPPLE}\,(\text{ESR})} \, = \, 1.07 \, \times \frac{1.6m}{2} \, = \, 0.856mV$$

$$V_{\text{RIPPLE}(c)} = \frac{1.07}{8 \times 14 \mu \times 580 k} = 16.5 \text{mV}$$

$$V_{\text{RIPPLE}} \ = \ \sqrt{16.5^2 \ + \ 0.856^2} \ = \ 16.52 mV$$

### **Input Capacitor Selection**

Since the input current of the buck converter is a pulsed discontinuous current, it is recommended to use a ceramic capacitor at the input to provide a pulsed input current thus keeping the DC input voltage stable. The ripple on the input capacitance of a ceramic capacitor can be calculated by the following equation:

$$V_{_{IN(Ripple)}} \approx D \times I_{_{OUT}} \times \frac{1 - D}{C_{_{IN}} \times f_{_{sw}}} + I_{_{OUT}} \times ESR$$

**Equation-13**

Where D =

$$\frac{V_{out}}{V_{in}}$$

In addition, since the input capacitance is a pulsed discontinuous current, the selected input capacitor must be able to withstand a large AC current:

$$I_{IN(RMS)} \approx I_{OUT(MAX)} \times \sqrt{D(1-D)}$$

Equation-14

In order to optimize the EMI performance of the chip and to ensure reliable and stable, it is recommended to add a 0.1µF ceramic capacitor (0603/0402 package) in addition to the ceramic capacitor as input capacitance C<sub>IN</sub>, and place it as close as possible to the VIN and GND pins of the chip. It should be noted that although ceramic capacitors have excellent high frequency performance and stable lifetime, in some hot-swap scenarios, the actual V<sub>IN</sub> voltage may oscillate due to the low ESR of the ceramic capacitors, and in the worst case, it may oscillate up to 2 times the V<sub>IN</sub> voltage, which can cause over-voltage breakdown of the chip. In this case, it is recommended to add an additional electrolytic capacitor with a larger ESR or a TVS diode in parallel with the input voltage to limit the input overvoltage.

| Table-1 Recor | nmended Com | ponent S | election | Table |

|---------------|-------------|----------|----------|-------|

|               |             |          |          |       |

| V <sub>OUT</sub> (V) | R <sub>FB(T)</sub> (kΩ) | $R_{FB(B)} \ (k\Omega)$ | L <sub>min</sub><br>(µH) | L <sub>typ</sub><br>(μΗ) | L <sub>max</sub><br>(µH) | C <sub>OUT(EFF)</sub> (μF) |

|----------------------|-------------------------|-------------------------|--------------------------|--------------------------|--------------------------|----------------------------|

| 5.0                  | 54.9                    | 10                      | 3.3                      | 4.7                      | 5.6                      | 10 to 68                   |

| 3.3                  | 33.2                    | 10                      | 2.2                      | 3.3                      | 4.7                      | 10 to 68                   |

| 2.5                  | 22.6                    | 10                      | 2.2                      | 2.2                      | 4.7                      | 20 to 68                   |

| 1.8                  | 13.7                    | 10                      | 1.5                      | 2.2                      | 4.7                      | 20 to 68                   |

| 1.5                  | 9.53                    | 10                      | 1.5                      | 1.5                      | 4.7                      | 20 to 68                   |

| 1.2                  | 5.76                    | 10                      | 1.2                      | 1.5                      | 4.7                      | 20 to 68                   |

| 1.05                 | 3.74                    | 10                      | 1.0                      | 1.5                      | 4.7                      | 20 to 68                   |

| 1                    | 3.09                    | 10                      | 1.0                      | 1.5                      | 4.7                      | 20 to 68                   |

#### **Feedforward Capacitor Selection**

PJ11027 utilizes the COT control architecture to ultra-fast load achieve transient response performance. In some applications where the load transient response is more demanding, the transient response can be further improved by adding a R<sub>FF</sub>, and a CFF, to the output feedback divider resistor. Considering the influence of noise coupling, it is recommended to use R<sub>FF</sub> = 2 k $\Omega$ ~10 k $\Omega$ , and do not use CFF higher than 100 pF. Note that the actual RFF and CFF are optional devices, and it is recommended to optimize the selection based on the results of the measured load transient response and the output tuning rate.

Figure-20. Feedforward Resistor and Capacitor

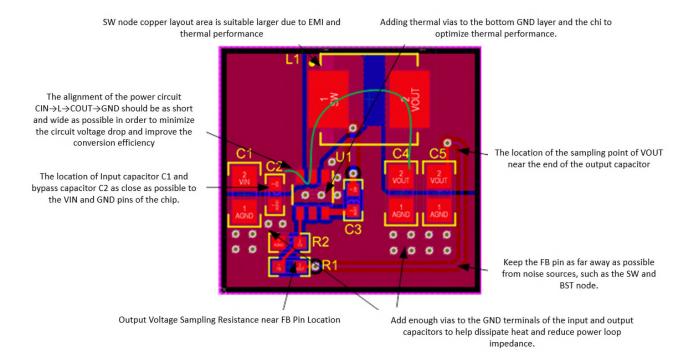

### **PCB Design Guidelines**

The stability of the device operation greatly depends on the PCB layout.

- 1. Position the ceramic capacitors as close to the VIN and GND pins as possible.

- Keep the alignment of the power circuit (CIN→L→ COUT→GND) as short and wide as possible to minimizes circuit voltage drop and enhances conversion efficiency.

- 3. The voltage waveform of the SW node forms a high-frequency square wave. Appropriately reducing the copper spreading of the SW node can enhance EMI performance. Conversely, increasing the spreading can optimize heat dissipation. The user should make the appropriate decision considering these factors based on the actual situation.

- Leave a considerable distance between the FB pin and noise sources like the SW node and BST node.

- Place the sampling point of the output voltage VOUT close to the end of the output capacitor, and position the voltage divider sampling resistor near the FB pin.

# PJ11027/F

# 18V, 2A, 600KHz High Efficiency Synchronous, Buck Converter In a SOT23-6 Package

Route and spread the copper of VIN and GND as wide as possible to help heat dissipation. In multilayer PCB design, it is recommended to have a complete GND layer for the GND pin and to add enough vias between the GND layer and the chip layer.

#### PCB design example is shown below:

Figure-21. PCB Design Example

### **Typical Reference Design**

Figure-22. V<sub>IN</sub>= 12V, V<sub>OUT</sub>= 5V, I<sub>OUT</sub>= 2A

Figure-23. V<sub>IN</sub>= 12V, V<sub>OUT</sub>= 3.3V, I<sub>OUT</sub>= 2A

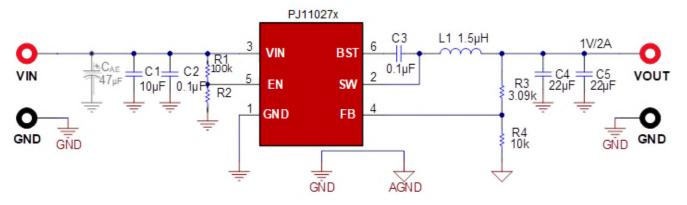

Figure-24.  $V_{IN}$ = 12V,  $V_{OUT}$ = 1.0V,  $I_{OUT}$ = 2A

Dec., 2023 REV.00 18

# **Typical Operating Characteristics**

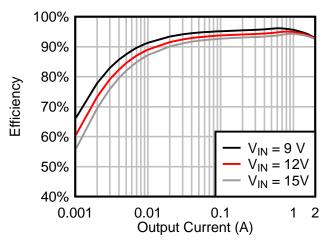

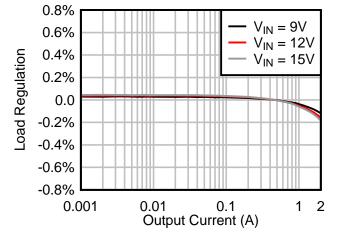

Test Conditions: V<sub>IN</sub> = 12V, V<sub>OUT</sub> = 5V, T<sub>A</sub> = 25°C (unless otherwise noted)

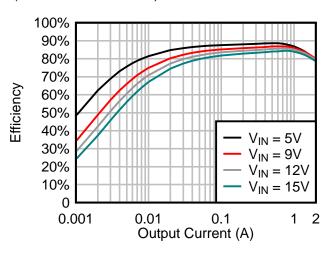

Figure-25. PJ11027 Vout = 5V Efficiency

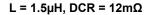

Figure-27. PJ11027 Load Regulation Vout = 5V

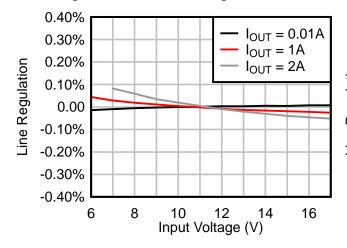

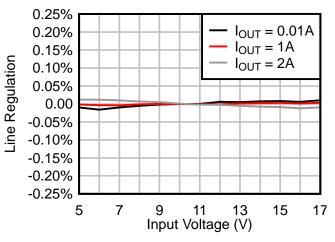

Figure-29. PJ11027 Line Regulation V<sub>OUT</sub> = 5V

Figure-26. PJ11027 Vout = 1.05V Efficiency

Figure-28. PJ11027 Load Regulation Vout = 1.05V

Figure-30. PJ11027 Line Regulation Vout = 1.05V

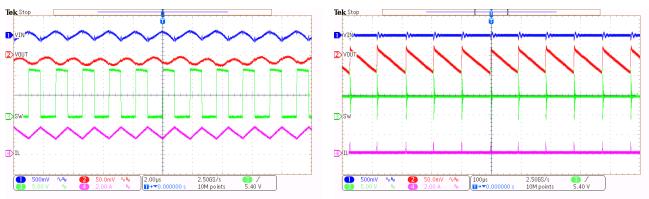

Test Conditions: V<sub>IN</sub> = 12V, V<sub>OUT</sub> = 5V, T<sub>A</sub> = 25°C (unless otherwise noted)

Figure-31. Input Ripple, IOUT = 2A

Figure-32. Output Ripple, IOUT = 10mA

Figure-33. Output Ripple, I<sub>OUT</sub> = 250mA

Figure-34. Output Ripple, I<sub>OUT</sub> = 1A

Figure-35. Output Ripple, IOUT = 2A

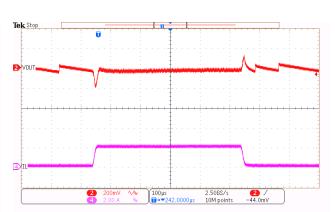

Figure-36. Load Transient, IOUT = 0A-2A, 250mA/µs

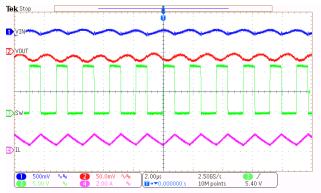

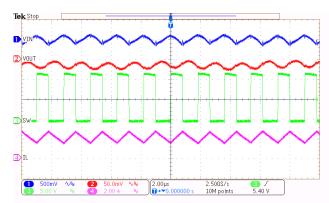

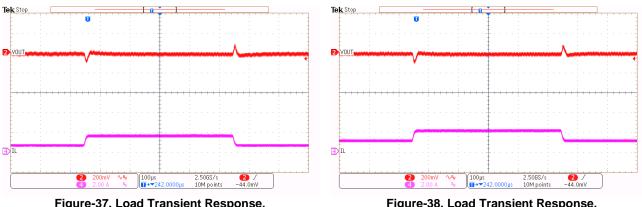

Test Conditions: V<sub>IN</sub> = 12V, V<sub>OUT</sub> = 5V, T<sub>A</sub> = 25°C (unless otherwise noted)

Figure-37. Load Transient Response, I<sub>OUT</sub> = 0.5A-1.5A, 250mA/µs

Figure-38. Load Transient Response, I<sub>OUT</sub> = 1A-2A, 250mA/µs

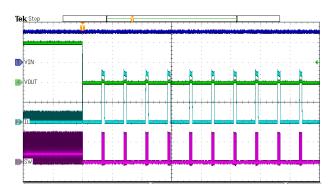

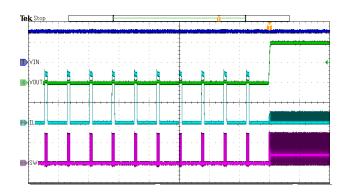

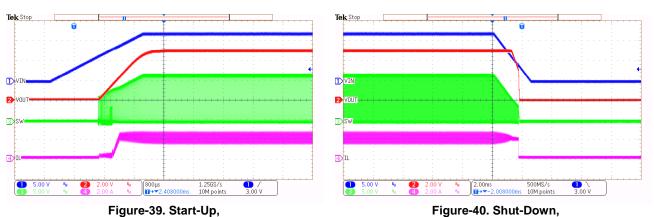

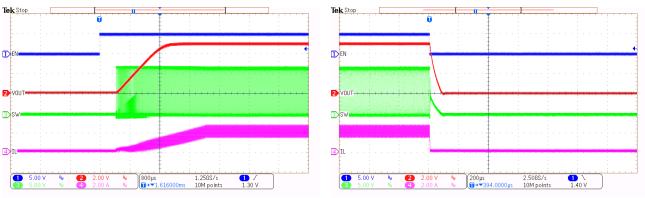

V<sub>IN</sub> = 12V, V<sub>OUT</sub> = 5V, I<sub>OUT</sub> = 2A

V<sub>IN</sub> = 12V, V<sub>OUT</sub> = 5V, I<sub>OUT</sub> = 2A

Figure-41. Start-Up,

$V_{IN} = 12V$ ,  $V_{OUT} = 5V$ ,  $I_{OUT} = 2A$

Figure-42. Shut-Down,  $V_{IN} = 12V$ ,  $V_{OUT} = 5V$ ,  $I_{OUT} = 2A$

Dec., 2023 REV.00 21

### **PACKAGE DIMENSION**

| Cumahad | Dimensio | ns (Millimeters) | Dimens      | ions (Inches) |

|---------|----------|------------------|-------------|---------------|

| Symbol  | Min.     | Max.             | Min.        | Max.          |

| А       | -        | 1.350            | -           | 0.053         |

| A1      | 0.000    | 0.150            | 0.000       | 0.006         |

| A2      | 1.000    | 1.200            | 0.039       | 0.047         |

| b       | 0.300    | 0.500            | 0.012       | 0.020         |

| С       | 0.100    | 0.220            | 0.004       | 0.009         |

| D       | 2.820    | 3.020            | 0.111       | 0.119         |

| Е       | 1.500    | 1.700            | 0.059       | 0.067         |

| E1      | 2.600    | 3.000            | 0.102       | 0.118         |

| е       | 0.9      | 50 (BSC)         | 0.037 (BSC) |               |

| e1      | 1.800    | 2.000            | 0.071       | 0.079         |

| L       | 0.300    | 0.600            | 0.012       | 0.024         |

| θ       | 0°       | 8°               | 0°          | 8°            |

### **Disclaimer**

- Reproducing and modifying information of the document is prohibited without permission from Panjit International Inc..

- Panjit International Inc. reserves the rights to make changes of the content herein the document anytime without notification. Please refer to our website for the latest document.

- Panjit International Inc. disclaims any and all liability arising out of the application or use of any product including damages incidentally and consequentially occurred.

- Panjit International Inc. does not assume any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

- Applications shown on the herein document are examples of standard use and operation. Customers are

responsible in comprehending the suitable use in particular applications. Panjit International Inc. makes no

representation or warranty that such applications will be suitable for the specified use without further testing or

modification.

- The products shown herein are not designed and authorized for equipments requiring high level of reliability or relating to human life and for any applications concerning life-saving or life-sustaining, such as medical instruments, transportation equipment, aerospace machinery et cetera. Customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Panjit International Inc. for any damages resulting from such improper use or sale.

- Since Panjit uses lot number as the tracking base, please provide the lot number for tracking when complaining