### **GENERAL DESCRIPTION**

The PJ67250 device, incorporating patented accurately measures technology, is a fully integrated, single-chip, pack-based solution that provides a rich array of features for gas gauging, protection, and authentication for 2-series, 3-series, and 4-series cell Li-Ion and Li-Polymer battery packs.

Using its integrated high-performance analog peripherals, the PJ67250 device measures and maintains an accurate record of available capacity, voltage, current, temperature, and other critical parameters in Li-lon or Li-Polymer batteries, and reports this information to the system host controller over an SMBus v3.1 compatible interface.

The PJ67250 device supports TURBO mode 3.0 by providing the available max power and max current to the host system. The device also supports Battery Trip Point to send a BTP interrupt signal to the host system at the pre-set state of charge thresholds.

The PJ67250 provides software-based 1st- and 2nd-level safety protection against over-voltage, under-voltage, overcurrent, short-circuit current, overload, and over-temperature conditions, as well as other pack- and cell- related faults.

SHA-1/SHA-256 and ECC authentication, with secure memory for authentication keys, enables identification of genuine battery packs.

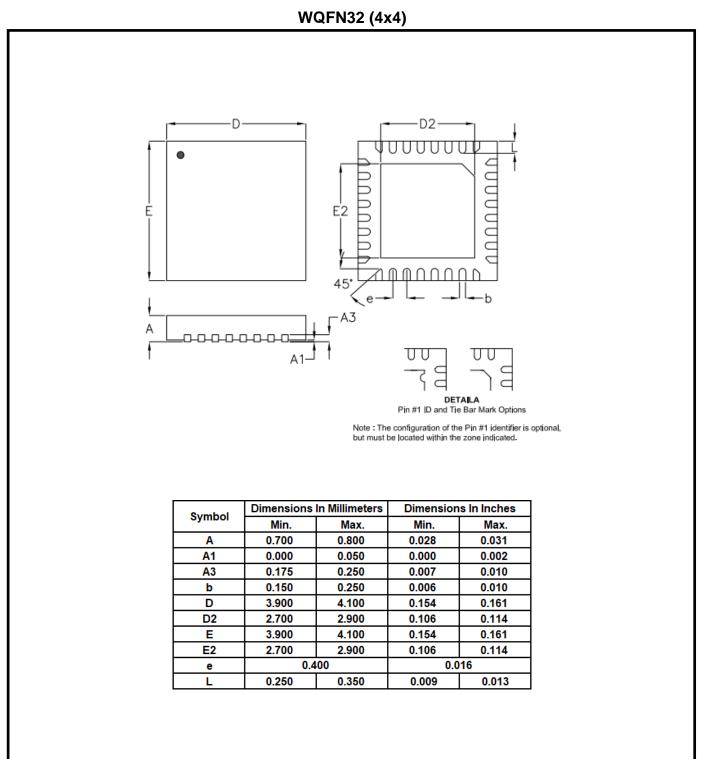

The compact 32-lead QFN package minimizes solution cost and size for smart batteries while providing maximum functionality and safety for battery gauging applications.

### **FEATURES**

- Fully Integrated 2-Series, 3-Series, and 4-Series

Li-Ion or Li-Polymer Cell Battery Pack Manager and

Protection

- Patented Accurately Measures Available Charge in Li-Ion and Li-Polymer Batteries

- High Side N-CH Protection FET Drive

- Integrated Cell Balancing While Charging or at Rest

- Full Array of Programmable Protection Features

- Voltage

- Current

- Temperature

- Charge Timeout

- CHG/DSG FETs

- AFE

- Sophisticated Charge Algorithms

- JEITA

- Enhanced Charging

- Adaptive Charging

- Cell Balancing

- Supports TURBO Mode 3.0

- Supports Battery Trip Point (BTP)

- Diagnostic Lifetime Data Monitor and Black Box Recorder

- LED Display

- Supports Two-Wire SMBus v3.1 Interface

- SHA-1/SHA-256, ECC Authentication

- Compact Package: 32-Lead QFN4x4

### **APPLICATIONS**

- Notebook / Tablets

- UPS and Battery Backup System

- Power Tools and Clean Robot

- Drone

## **ORDERING INFORMATION**

| ORDER NUMBER | Marking ID   | Package   | Description                        |

|--------------|--------------|-----------|------------------------------------|

| PJ67250QW_R1 | A1 YM<br>DNN | QFN4x4-32 | Halogen Free in T&R, 3000 pcs/Reel |

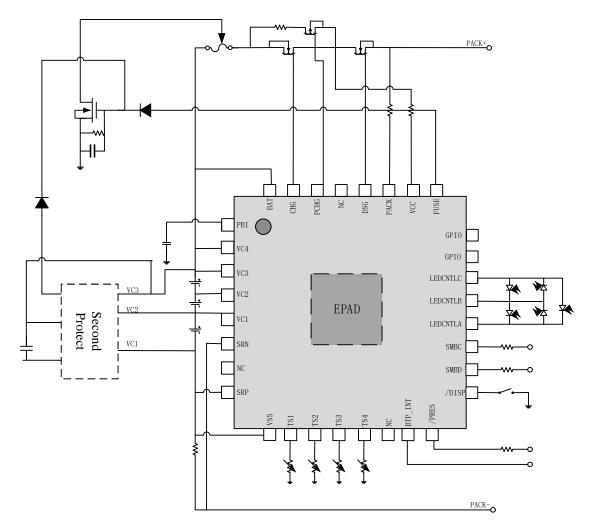

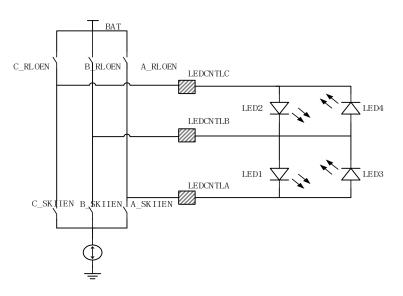

## SIMPLE SCHEMATIC

Figure-1. PJ67250 Simple Schematic

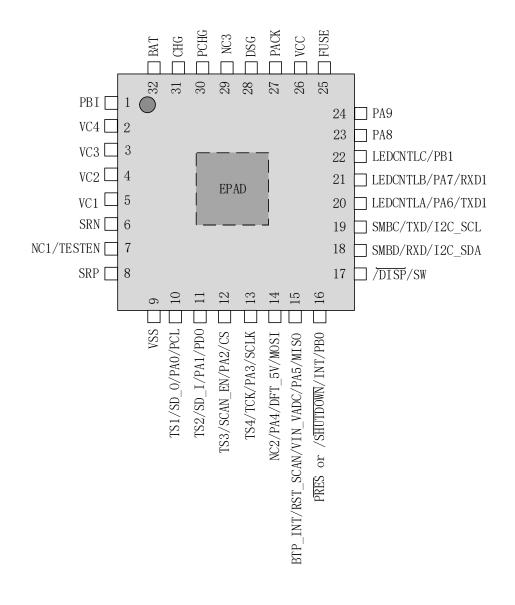

## **PIN CONFIGURATION**

### (TOP VIEW)

## 2-Series, 3-Series, and 4-Series Li-Ion Battery Pack Manager In a QFN4x4-32 Package

## **FUNCTIONAL PIN DESCRIPTION**

| TERMINAL |         | PIN  |                                                                                                                                                                      |  |  |  |

|----------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NUMBER   | NAME    | TYPE | DESCRIPTION                                                                                                                                                          |  |  |  |

| 1        | PBI     | Р    | Power supply backup input pin                                                                                                                                        |  |  |  |

| 2        | VC4     | I    | Sense voltage input pin for most positive cell, and balance current input for most positive cell                                                                     |  |  |  |

| 3        | VC3     | I    | Sense voltage input pin for second most positive cell, balance current input for second most positive cell, and return balance current for most positive cell        |  |  |  |

| 4        | VC2     | I    | Sense voltage input pin for third most positive cell, balance current input for third most positive cell, and return balance current for second most positive cell   |  |  |  |

| 5        | VC1     | I    | Sense voltage input pin for least positive cell, balance current input for least positive cel<br>and return balance current for third most positive cell             |  |  |  |

| 6        | SRN     | I    | Analog input pin connected to the internal coulomb counter peripheral for integrating small voltage between SRP and SRN where SRP is the top of the sense resistor   |  |  |  |

| 7        | NC1     | -    | Not internally connected, it can connect to ground                                                                                                                   |  |  |  |

| 7        | TESTEN  | I    | TESTEN pin for DFT                                                                                                                                                   |  |  |  |

| 8        | SRP     | I    | Analog input pin connected to the internal coulomb counter peripheral for integrating a small voltage between SRP and SRN where SRP is the top of the sense resistor |  |  |  |

| 9        | VSS     | Р    | Device Ground                                                                                                                                                        |  |  |  |

|          | TS1     | I    | Temperature sensor 1 thermistor input pin                                                                                                                            |  |  |  |

| 10       | SD_0    | I/O  | SD_0 pin of DFT                                                                                                                                                      |  |  |  |

| 10       | PA0     | I/O  | General purpose GPIO                                                                                                                                                 |  |  |  |

|          | PCL     | I/O  | PCL pin of SWD                                                                                                                                                       |  |  |  |

|          | TS2     | I    | Temperature sensor 2 thermistor input pin                                                                                                                            |  |  |  |

| 11       | SD_I    | I/O  | SD_I pin of DFT                                                                                                                                                      |  |  |  |

| 11       | PA1     | I/O  | General purpose GPIO                                                                                                                                                 |  |  |  |

|          | PDO     | I/O  | PDO pin of SWD                                                                                                                                                       |  |  |  |

|          | TS3     | I    | Temperature sensor 3 thermistor input pin                                                                                                                            |  |  |  |

| 12       | SCAN_EN | I    | SCAN_EN pin of DFT                                                                                                                                                   |  |  |  |

| 12       | PA2     | I/O  | General purpose GPIO                                                                                                                                                 |  |  |  |

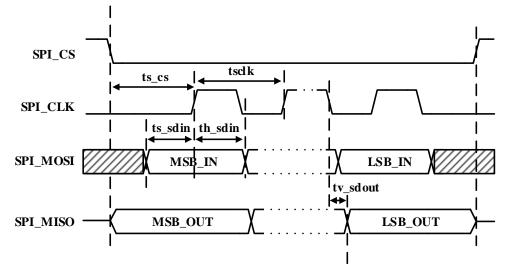

|          | CS      | I    | Chip Select pin of SPI, pull it high , when it was selected                                                                                                          |  |  |  |

| TERMINAL |                     | PIN  | DESCRIPTION                                                                                          |

|----------|---------------------|------|------------------------------------------------------------------------------------------------------|

| NUMBER   | NAME                | TYPE | DESCRIPTION                                                                                          |

|          | TS4                 | I    | Temperature sensor 4 thermistor input pin                                                            |

| 13       | ТСК                 | I    | TCK pin of DFT                                                                                       |

| 13       | PA3                 | I/O  | General purpose GPIO                                                                                 |

|          | SCLK                | I    | Clock pin of SPI                                                                                     |

|          | NC2                 | -    | Not internally connected                                                                             |

| 14       | DFT_5V              | I    | Enable pin of DFT_5V                                                                                 |

| 14       | PA4                 | I/O  | General purpose GPIO                                                                                 |

|          | MOSI                | 0    | Host data output, slave data input signal                                                            |

|          | BTP_INT             | 0    | Power Ground. PGND requires extra care during PCB layout. Connect to GND with copper traces and vias |

|          | RST_SCAN            | I    | Reset scan pin of DFT                                                                                |

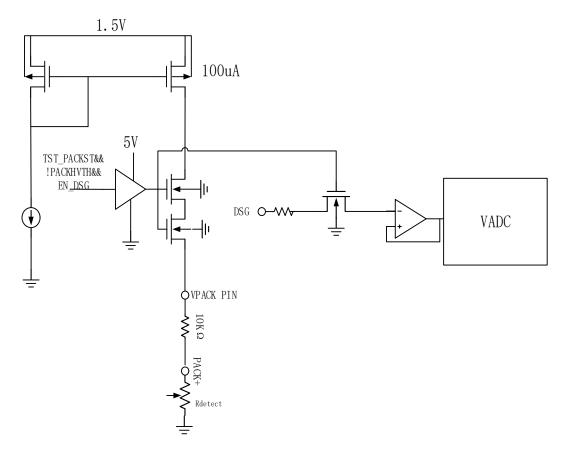

| 15       | VIN_VADC            | I    | VADC input                                                                                           |

|          | SP5                 | I/O  | General purpose GPIO                                                                                 |

|          | MISO                | I    | The host data input, slave data output signal                                                        |

|          | /PRES or<br>/SHUTDN | ο    | Current monitor output                                                                               |

| 16       | PB0                 | I/O  | General purpose GPIO                                                                                 |

|          | INT                 | 0    | Interrupt output of AFE                                                                              |

| 17       | DISP                | -    | EN input. Apply logic high to enable the chip                                                        |

| 17       | SW                  | 0    | Interrupt wakes up the chip from Shutdown                                                            |

|          | SMBD                | I/O  | SMBus data pin                                                                                       |

| 18       | RXD                 | I/O  | Receiver terminal of UART                                                                            |

|          | I2C_SDA             | I    | Data input of I2C interface                                                                          |

|          | SMBC                | I/O  | SMBus clock pin                                                                                      |

| 19       | TXD                 | I/O  | Transmitter terminal of UART                                                                         |

|          | I2C_SCL             | I    | Clock input of I2C                                                                                   |

| TERMINAL |          | PIN  | DESCRIPTION                                                                                                  |

|----------|----------|------|--------------------------------------------------------------------------------------------------------------|

| NUMBER   | NAME     | TYPE | DESCRIPTION                                                                                                  |

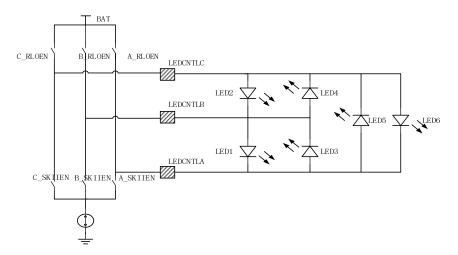

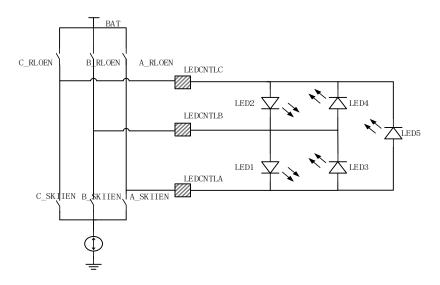

|          | LEDCNTLA | I/O  | LED display control pin                                                                                      |

| 20       | PA6      | I/O  | General purpose GPIO                                                                                         |

| TXD1     |          | I/O  | Transmitter1 terminal of UART                                                                                |

|          | LEDCNTLB | I/O  | LED display control pin                                                                                      |

| 21       | PA7      | I/O  | General purpose GPIO                                                                                         |

|          | RXD1     | I/O  | Receiver1 terminal of UART                                                                                   |

| 22       | LEDCNTLC | I/O  | LED display control pin                                                                                      |

| 22       | PB1      | I/O  | General purpose GPIO                                                                                         |

| 23       | PA8      | I/O  | PTC, Safety PTC thermistor input pin. To disable, connect both PTC and PTCEN to VSS                          |

| 24       | PA9      | I/O  | PTCEN, Safety PTC thermistor enable input pin. Connect to BAT. To disable, connect both PTC and PTCEN to VSS |

| 25       | FUSE     | 0    | Fuse drive output pin                                                                                        |

| 26       | VCC      | Р    | Secondary power supply input                                                                                 |

| 27       | PACK     | I    | Pack sense input pin                                                                                         |

| 28       | DSG      | 0    | NMOS Discharge FET drive output pin                                                                          |

| 29       | NC3      | -    | Not internally connected                                                                                     |

| 30       | PCHG     | 0    | PMOS Precharge FET drive output pin                                                                          |

| 31       | CHG      | 0    | NMOS Charge FET drive output pin                                                                             |

| 32       | BAT      | Р    | Primary power supply input pin                                                                               |

## **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                                           | PARAMETER                                     | MIN                | MAX | Unit |

|-------------------------------------------|-----------------------------------------------|--------------------|-----|------|

|                                           | BAT, VCC, PBI                                 | -0.3 30<br>-0.3 30 | V   |      |

|                                           | PACK, PA6, PA7, PA8, PA9, PB1                 | -0.3               | 30  | V    |

|                                           | PA0, PA1, PA2, PA3, PA4, PA5, PB0, SW, TESTEN | -0.3               | 3.6 | V    |

|                                           | SRP, SRN                                      | -0.3               | 3.5 | V    |

|                                           | VC4                                           | VC3 - 0.3          |     | V    |

| Voltage range at terminals <sup>(2)</sup> | VC3                                           | VC2 - 0.3          |     | V    |

|                                           | VC2                                           | VC1 - 0.3          |     | V    |

|                                           | VC1                                           | VSS - 0.3          |     | V    |

|                                           | CHG, DSG, VBMC                                | -0.3               | 32  | V    |

|                                           | PCHG, SDSG                                    | -0.3               | 30  | V    |

| Current Range                             | VSS source Current                            |                    | 50  | mA   |

| TJ                                        | Operating junction temperature range          | -40                | 150 | °C   |

| Тѕтс                                      | Storage temperature range                     | -65                | 150 | °C   |

(1) Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground terminal.

## HANDLING RATINGS

| PARAMETER          | DEFINITION                                                              | MIN | MAX | UNIT |

|--------------------|-------------------------------------------------------------------------|-----|-----|------|

| ESD <sup>(1)</sup> | Human body model (HBM) ESD stress voltage <sup>(2)</sup>                | -2  | 2   | kV   |

|                    | Charged device model (CDM) ESD stress voltage <sup>(3)</sup> , all pins | -1  | 1   | kV   |

(1) Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges into the device.

(2) Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(3) Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## **RECOMMENDED OPERATING CONDITIONS**

|                  | F                           | PARAMETER                            | MIN              | ТҮР  | MAX                 | UNIT |

|------------------|-----------------------------|--------------------------------------|------------------|------|---------------------|------|

| Vcc              | Supply voltage              | BAT, VCC, PBI                        | 4.4              |      | 26                  | V    |

| Vshutdown-       | Shutdown voltage            | VPACK < VSHUTDOWN-                   | 1.75             | 2.2  | 2.6                 | V    |

| VSHUTDOWN+       | Start-up voltage            | VPACK > VSHUTDOWN- + VHYS            | 2.05             | 2.45 | 2.85                | V    |

| V <sub>HYS</sub> | Shutdown voltage hysteresis | VSHUTDOWN+ - VSHUTDOWN-              |                  | 250  |                     | mV   |

|                  |                             | PACK, SMBC, SMBD, PRES, BTP_IN, DISP |                  |      | 26                  |      |

|                  | Input voltage<br>range      | TS1, TS2, TS3, TS4                   |                  |      | Vreg                |      |

|                  |                             | LEDCNTLA, LEDCNTLB, LEDCNTLC         |                  |      | Vbat                |      |

| Vin              |                             | SRP, SRN                             | -0.2             |      | 0.2                 | V    |

|                  |                             | VC4                                  | V <sub>VC3</sub> |      | V <sub>VC3</sub> +5 |      |

|                  |                             | VC3                                  | V <sub>VC2</sub> |      | V <sub>VC2</sub> +5 |      |

|                  |                             | VC2                                  | V <sub>VC1</sub> |      | V <sub>VC1</sub> +5 |      |

|                  |                             | VC1                                  | V <sub>VSS</sub> |      | V <sub>VSS</sub> +5 |      |

| Vo               | Output voltage range        | CHG, DSG, PCHG, FUSE                 |                  |      | 26                  | V    |

| Срві             | External PBI capacitor      |                                      | 2.2              |      |                     | uF   |

| Topr             | Operating<br>temperature    |                                      | -40              |      | 85                  | °C   |

## **THERMAL INFORMATION**

|                                | THERMAL RESISTANCE                                | WQFN-32 (4mm x 4mm) | UNIT |

|--------------------------------|---------------------------------------------------|---------------------|------|

| Θ <sub>JA</sub> <sup>(1)</sup> | Junction to ambient thermal resistance (JESD51-7) | 46.8                | °C/W |

| ΘJC(top)                       | Junction to case (top) thermal resistance         | 19.5                | °C/W |

| Θ <sub>JB</sub>                | Junction to board thermal resistance              | 14.7                | °C/W |

| Ψյт                            | Junction to top characterization parameter        | 0.8                 | °C/W |

| ΨJB                            | Junction to board characterization parameter      | 14.4                | °C/W |

| ΘJC(bottom)                    | Junction to case (bottom) thermal resistance      | 3.8                 | °C/W |

(1) Measured on JESD51-7, 4-layer PCB.

## **ELECTRICAL CHARACTERISTICS**

#### $T_J$ = -40°C to 85°C, $V_{IN}$ = 14.4V. Typical value is tested at $T_J$ = +25°C, unless otherwise noted.

|                          | PARAMETER                                             | TEST CONDITIONS                       | MIN   | TYP    | MAX   | UNIT |

|--------------------------|-------------------------------------------------------|---------------------------------------|-------|--------|-------|------|

| SUPPLY Cur               | rent - V <sub>CC</sub> = 4.4V to 26V                  |                                       |       |        |       |      |

| INORMAL                  | NORMAL mode                                           | CHG on. DSG on, no Flash write        |       | 400    | 600   | uA   |

|                          |                                                       | CHG off, DSG on, no SMBus (5S/ test)  |       | 80     | 120   | uA   |

| ISLEEP                   | SLEEP mode                                            | CHG off, DSG on, no SMBus (3S/ test)  |       | 88     | 132   | uA   |

|                          |                                                       | CHG off, DSG off, no SMBus (5S/ test) |       | 52     | 78    | uA   |

| ISHUTDOWN                | SHUTDOWN mode                                         | When $T_J = 85^{\circ}C$ , <10uA      |       | 7      | 10    | uA   |

| Power Suppl              | <b>y Control -</b> V <sub>CC</sub> = 4.4V to 26       | l<br>V                                |       |        |       |      |

| V <sub>SWITCHOVER-</sub> | BAT to Vcc switchover voltage                         | VBUS > VSWITCHOVER-                   | 2.6   | 3.1    | 3.6   | V    |

| $V_{\text{SWITCHOVER+}}$ | Vcc to BAT switchover voltage                         | VBUS < VSWITCHOVER- + VHYS            | 2.25  | 2.85   | 3.4   | V    |

| VHYS                     | Switchover voltage hysteresis                         | Vswitchover+ – Vswitchover-           |       | 250    |       | mV   |

| AFE Power-C              | <b>On Reset -</b> V <sub>CC</sub> = 4.4V to 26V       | /                                     |       |        |       |      |

| V <sub>REG</sub>         | AFE Voltage                                           | V <sub>REG</sub>                      | 1.95  | 2      | 2.05  | V    |

| V <sub>REGIT-</sub>      | Negative-going voltage input                          | V <sub>REG</sub>                      | 1.7   | 1.8    | 1.9   | V    |

| V <sub>HYS</sub>         | Power-on reset<br>hysteresis                          | VREGIT+ – VREGIT–                     | 70    | 100    | 130   | m۷   |

| t <sub>RST</sub>         | Power-on reset time                                   |                                       | 200   | 300    | 400   | uS   |

| AFE Watchde              | og Reset and Wake Time                                | <b>r</b> - $V_{CC} = 4.4V$ to 26V     |       |        |       |      |

|                          |                                                       | t <sub>WDT</sub> = 500                | 372   | 500    | 628   | - mS |

|                          |                                                       | t <sub>WDT</sub> = 1000               | 744   | 1,000  | 1256  |      |

| t <sub>WDT</sub>         | AFE watchdog timeout                                  | t <sub>WDT</sub> = 2000               | 1,488 | 2,000  | 2,512 |      |

|                          |                                                       | t <sub>WDT</sub> = 4000               | 2,976 | 4,000  | 5,024 |      |

|                          |                                                       | t <sub>WAKE</sub> = 250               | 186   | 250    | 314   |      |

|                          |                                                       | t <sub>WAKE</sub> = 500               | 372   | 500    | 628   | ]    |

| t <sub>WAKE</sub>        | AFE wake timer                                        | t <sub>WAKE</sub> = 1000              | 744   | 1,000  | 1,256 | – mS |

|                          |                                                       | t <sub>WAKE</sub> = 2000              | 1,488 | 2,000  | 2,512 | -    |

| t <sub>FETOFF</sub>      | FET off delay after reset                             | t <sub>FETOFF</sub> = 512             | 409   | 512    | 614   | mS   |

| Current Wak              | e Comparator - V <sub>CC</sub> = 4.4V                 | to 26V                                |       |        |       |      |

|                          |                                                       | $V_{WAKE} = \pm 0.625 \text{ mV}$     | ±0.3  | ±0.625 | ±0.9  |      |

|                          |                                                       | $V_{WAKE} = \pm 1.25 \text{ mV}$      | ±0.6  | ±1.25  | ±1.8  | 1.   |

| Vwake                    | Wake voltage threshold                                | $V_{WAKE} = \pm 2.5 \text{ mV}$       | ±1.2  | ±2.5   | ±3.6  | — mV |

|                          |                                                       | V <sub>WAKE</sub> = ±5 mV             | ±2.4  | ±5.0   | ±7.2  |      |

| $V_{WAKE(DRIFT)}$        | Temperature drift of<br>V <sub>WAKE</sub> accuracy    |                                       |       | 0.5%   |       | °C   |

| t <sub>WAKE</sub>        | Time from application of<br>current to wake interrupt |                                       |       |        | 700   | μS   |

|                       | PARAMETER                                   | TEST CONDITIONS                                                                       | MIN                             | TYP   | MAX                   | UNIT |

|-----------------------|---------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------|-------|-----------------------|------|

| $t_{\text{WAKE(SU)}}$ | Wake comparator startup time                |                                                                                       | 500                             | 1,000 |                       | μS   |

| VC1, VC2, V           | VC3, VC4, BAT, PACK - V <sub>ct</sub>       | c = 4.4V to 26V                                                                       | I                               |       |                       | I    |

|                       |                                             | VC1 - VSS, VC2 - VC1, VC3 - VC2, VC4 - VC3                                            | 0.198                           | 0.2   | 0.202                 | <br> |

| к                     | Scaling factor                              | BAT - VSS, PACK - VSS                                                                 | 0.049                           | 0.05  | 0.051                 | _    |

|                       |                                             | VREF2                                                                                 | 0.49                            | 0.5   | 0.51                  |      |

| M                     |                                             | VC1 - VSS, VC2 - VC1, VC3 - VC2, VC4 - VC3                                            | - 0.2                           |       | 5                     | v    |

| V <sub>IN</sub>       | Input voltage range                         | BAT - VSS, PACK - VSS                                                                 | - 0.2                           |       | 20                    | v    |

| I <sub>LKG</sub>      | Input leakage current                       | VC1, VC2, VC3, VC4 cell balancing off, cell detach detection off, ADC multiplexer off |                                 |       | 1                     | μA   |

| I <sub>CB</sub>       | Internal cell balance current               | IDS(ON) internal switching current, when $2V < V_{DS} < 4 V$                          | 2                               |       | 20                    | mA   |

| I <sub>CD</sub>       | Internal cell detach<br>check current       | VCx > VSS + 0.8 V                                                                     | 30                              | 50    | 70                    | μA   |

| HV GPIO (P            | <b>PA1) -</b> V <sub>CC</sub> = 4.4V to 26V |                                                                                       |                                 |       |                       |      |

| V <sub>OH</sub>       | Output voltage high                         | I <sub>OH</sub> = 1.5 mA                                                              | 3                               |       |                       | V    |

| V <sub>OL</sub>       | Output voltage low                          | I <sub>OL</sub> = 1.5 mA                                                              |                                 |       | 0.4                   | V    |

| C <sub>IN</sub>       | Input capacitance                           |                                                                                       |                                 | 5     |                       | pF   |

| I <sub>LKG</sub>      | Input leakage current                       |                                                                                       |                                 |       | 1                     | μA   |

| R <sub>PD</sub>       | Pulldown resistance                         | V <sub>DD</sub> =3.3V                                                                 | 42                              | 60    | 78                    | ΚΩ   |

| HV GPIO SI            | <b>MBus -</b> V <sub>CC</sub> = 4.4V to 26V |                                                                                       |                                 |       |                       |      |

|                       | Input voltage high                          | V <sub>REG</sub> = 1.8 V                                                              | 1.26                            |       |                       | V    |

| Vih                   | (SMBus,I2C)                                 | V <sub>REG</sub> = 1.2 V                                                              | 0.96                            |       |                       | V    |

|                       | Input voltage high<br>(UART)                | V <sub>DD</sub> = 3.3V                                                                | 0.7xV <sub>DD</sub>             |       |                       | V    |

|                       | Input voltage Low                           | V <sub>REG</sub> = 1.8 V                                                              |                                 |       | 0.54                  | V    |

| VIL                   | (SMBus,I2C)                                 | V <sub>REG</sub> = 1.2 V                                                              |                                 |       | 0.4                   | V    |

|                       | Input voltage Low<br>(UART)                 | V <sub>DD</sub> = 3.3V                                                                |                                 |       | $0.3 x V_{\text{DD}}$ | V    |

| V <sub>OH</sub>       | Output voltage high                         | I <sub>OH</sub> = 3mA                                                                 | 3                               |       |                       | V    |

| Vol                   | Output voltage low                          | I <sub>OL</sub> = 3mA                                                                 |                                 |       | 0.4                   | V    |

| C <sub>IN</sub>       | Input capacitance                           |                                                                                       |                                 | 5     |                       | pF   |

| I <sub>LKG</sub>      | Input leakage current                       |                                                                                       |                                 |       | 1                     | μA   |

| Rph                   | Pull-up resistance                          | V <sub>DD</sub> = 3.3V                                                                | 48                              | 60    | 72                    | ΚΩ   |

| R <sub>PD</sub>       | Pull-down resistance                        | V <sub>DD</sub> = 3.3V                                                                | 42                              | 60    | 78                    | KΩ   |

| GPIO (PA0,            | PA1, PA2, PA3, PA4, PA5                     | , PA6, PA7, PA8, PA9, PB0, SW) - $V_{CC} = 4.4 V$ to                                  | 26V                             |       |                       |      |

| VIH                   | Input voltage high                          | V <sub>DD</sub> =3.3V                                                                 | $0.7 \mathrm{xV}_{\mathrm{DD}}$ |       |                       | V    |

| VIL                   | Input voltage low                           |                                                                                       |                                 |       | $0.3 x V_{\text{DD}}$ | V    |

| V <sub>OH</sub>       | Output voltage high                         | Input voltage high                                                                    | 3                               |       |                       | V    |

| V <sub>OL</sub>       | Output voltage low                          | IOL=1.5mA                                                                             |                                 |       | 0.4                   | V    |

| F                          | PARAMETER                             | TEST CONDITIONS                                      | MIN                   | ТҮР   | MAX                       | UNIT       |

|----------------------------|---------------------------------------|------------------------------------------------------|-----------------------|-------|---------------------------|------------|

| CIN                        | Input capacitance                     |                                                      |                       | 5     |                           | pF         |

| I <sub>LKG</sub>           | Input leakage current                 |                                                      |                       |       | 1                         | μA         |

| R <sub>PH</sub>            | Pull-up resistance                    | V <sub>DD</sub> = 3.3V                               | 48                    | 60    | 72                        | ΚΩ         |

| R <sub>PD</sub>            | Pull-down resistance                  | V <sub>DD</sub> = 3.3V                               | 42                    | 60    | 78                        | ΚΩ         |

| LED Display                | • V <sub>CC</sub> = 4.4V to 26V       | I                                                    |                       |       |                           |            |

| V <sub>IH</sub>            | Input voltage high                    |                                                      | 1.45                  |       |                           | V          |

| VIL                        | Input voltage low                     |                                                      |                       |       | 0.55                      | V          |

| V <sub>OH</sub>            | Output voltage high                   | V <sub>BAT</sub> > 3.0 V, I <sub>OH</sub> = -22.5 mA | V <sub>BAT</sub> -1.6 |       |                           | V          |

| V <sub>OL</sub>            | Output voltage low                    | l <sub>ol</sub> = 1.5 mA                             |                       |       | 0.4                       | V          |

| I <sub>SC</sub>            | High level output current protection  |                                                      | -30                   | -45   | -60                       | mA         |

| IOL                        | Low level output current              | V <sub>BAT</sub> > 3.6 V, V <sub>OH</sub> = 0.4 V    | 15.75                 | 22.5  | 29.25                     | mA         |

| ILEDCNTLX                  | Current matching between LEDCNTLx     | V <sub>BAT</sub> >3.6 V                              |                       | ±1    |                           | %          |

| C <sub>IN</sub>            | Input capacitance                     |                                                      |                       | 20    |                           | pF         |

| I <sub>LKG</sub>           | Input leakage current                 |                                                      |                       |       | 1                         | μA         |

| fledcntlx                  | Frequency of LED pattern              |                                                      |                       | 124   |                           | Hz         |

| Coulomb Cou                | <b>Inter -</b> $V_{CC} = 4.4V$ to 26V |                                                      |                       |       |                           | 1          |

| Input voltage ra           | nge                                   |                                                      | - 0.1                 |       | 0.1                       | V          |

| Full scale range           |                                       |                                                      | V <sub>REF1</sub> /10 |       | V <sub>REF1</sub> /10     | V          |

| Integral nonlinea          | arity                                 | 16-bit, best fit over input voltage range            | ±5.2                  |       | ±22.3                     | LSB        |

| Offset error               |                                       | 16-bit, Post-calibration                             |                       | ±2.5  | ±5                        | μV         |

| Offset error drift         |                                       | 16-bit + sign, Post-calibration                      |                       | 0.2   | 0.3                       | µV/<br>°C  |

| Gain error                 |                                       | 16-bit + sign, over input voltage range              |                       | ±0.2% | ±0.8%                     | FSR        |

| Gain error drift           |                                       | 16-bit + sign, over input voltage range              |                       | 30    | 150                       | PPM/<br>°C |

| Effective input re         | esistance                             |                                                      | 2.5                   |       |                           | MΩ         |

| Conversion time            | )                                     | Single conversion                                    |                       | 250   |                           | mS         |

| Effective resolut          | ion                                   | Single conversion                                    | 16                    |       |                           | Bits       |

| VADC - V <sub>CC</sub> = 4 | 4.4V to 26V                           | 1                                                    | ı                     |       |                           | ·          |

|                            |                                       | Internal reference (VREF1)                           | -0.2                  |       | 1                         |            |

| Input voltage ra           | nge                                   | External reference (VREG)                            | -0.2                  |       | 0.8 ×<br>V <sub>REG</sub> | V          |

| Full scale range           | 1                                     | VFS = VREF1 or VREG                                  | -V <sub>FS</sub>      |       | V <sub>FS</sub>           | V          |

| late and a 2               |                                       | 16-bit, Input Range -0.1 V~0.8 × VREF1               |                       |       | ±6.6                      | 1.05       |

| Integral nonlinea          | arity                                 | 16-bit, Input Range -0.2 V ~ -0.1 V                  |                       |       | ±13.1                     | LSB        |

| P                     | ARAMETER                                | TEST CONDITIONS                                                                                                                                                                                                                   | MIN   | ТҮР   | МАХ   | UNIT       |

|-----------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------------|

| Offset error          |                                         | 16-bit, Post-calibration, VFS = VREF1                                                                                                                                                                                             |       | ±67   | ±157  | μV         |

| Offset error drift    |                                         | 16-bit, Post-calibration, VFS = VREF1                                                                                                                                                                                             |       | 0.6   | 3     | µV/<br>°C  |

| Gain error            |                                         | 16-bit, -0.1 V to 0.8 × VFs                                                                                                                                                                                                       |       | ±0.2% | ±0.8% | FSR        |

| Gain error drift      |                                         | 16-bit, -0.1 V to 0.8 × VFS                                                                                                                                                                                                       |       |       | 30    | PPM/<br>°C |

| Effective input re    | esistance                               |                                                                                                                                                                                                                                   | 8     |       |       | MΩ         |

|                       |                                         | Single conversion                                                                                                                                                                                                                 |       | 31.25 |       |            |

| Conversion time       |                                         | Single conversion                                                                                                                                                                                                                 |       | 15.63 |       |            |

| Conversion time       |                                         | Single conversion                                                                                                                                                                                                                 |       | 7.81  |       | mS         |

|                       |                                         | Single conversion                                                                                                                                                                                                                 |       | 1.95  |       |            |

| Resolution            |                                         | No missing codes                                                                                                                                                                                                                  | 16    |       |       | Bits       |

| Effective resolution  |                                         | With sign, tCONV = 31.25mS                                                                                                                                                                                                        | 15    | 16    |       |            |

|                       |                                         | With sign, tCONV = 15.63mS                                                                                                                                                                                                        | 14    | 15    |       | Bits       |

|                       |                                         | With sign, tCONV = 7.81mS                                                                                                                                                                                                         | 12    | 13    |       |            |

|                       |                                         | With sign, tCONV = 1.95mS                                                                                                                                                                                                         | 10 11 |       |       |            |

| CHG, DSG FE           | <b>T Drive -</b> $V_{CC} = 4.4V$ to 26V |                                                                                                                                                                                                                                   |       |       |       |            |

|                       |                                         | $\begin{array}{l} \mbox{Ratio}_{\mbox{CHG}} = \ (V_{\mbox{CHG}} - V_{\mbox{BAT}}) \ /V_{\mbox{BAT}}, \ 4.4V < V_{\mbox{BAT}} < \\ \ 4.8V \ , \ 10 \ M\Omega \ between \ BAT \ and \ CHG \end{array}$                              |       | 2.333 |       | _          |

| Output voltage r      | atio                                    | $\label{eq:Ratio} \begin{split} \text{Ratio}_{\text{DSG}} = (V_{\text{DSG}} - V_{\text{BAT}})/V_{\text{BAT}}, \ 4.4V < V_{\text{BAT}} < 4.8V, \\ 10 \ \text{M}\Omega \ \text{between PACK} \ \text{and} \ \text{DSG} \end{split}$ |       | 2.333 |       | _          |

|                       |                                         | $\label{eq:Ratio_VBMC} \begin{array}{l} \mbox{Ratio}_{VBMC} = \ (V_{BMC} - V_{BAT}) \ /V_{BAT}, \ 4.4V < V_{BAT} < \\ \ 4.8V \ , \ 10 \ M\Omega \ between \ PACK \ and \ BMC \end{array}$                                         |       | 2.333 |       | _          |

|                       |                                         | Ratio_{CHG} = V_{CHG} - V_{BAT}, 4.8 < V_{BAT} , 10 M $\Omega$ between BAT and CHG                                                                                                                                                | 9     | 11    | 12.5  | V          |

| V <sub>(FETON)</sub>  | Output voltage, CHG and DSG on          | Ratio <sub>DSG</sub> = $V_{DSG} - V_{BAT}$ , 4.8 < $V_{BAT}$ , 10 M $\Omega$<br>between PACK and DSG                                                                                                                              | 9     | 11    | 12.5  | V          |

|                       |                                         | RatioV <sub>BMC</sub> = V <sub>BMC</sub> - V <sub>BAT</sub> , 4.8 < V <sub>BAT</sub> , 10 MΩ between PACK and BMC                                                                                                                 | 9     | 11    | 12.5  | V          |

|                       |                                         | $V_{\text{DSG(OFF)}}$ = $V_{\text{DSG}}$ – $V_{\text{PACK}},$ 10 M $\Omega$ between PACK and DSG                                                                                                                                  | -0.4  |       | 0.4   | V          |

| $V_{(FETOFF)}$        | Output voltage, CHG and DSG off         | $V_{CHG(OFF)}$ = $V_{CHG}~-~V_{BAT,}$ 10 M $\Omega$ between PACK and BMC                                                                                                                                                          | -0.4  |       | 0.4   | v          |

|                       |                                         | $V_{\text{BMC(OFF)}}$ = $V_{\text{BMC}}$ – $V_{\text{BUS}},$ 10 M $\Omega$ between PACK and BMC                                                                                                                                   | -0.4  |       | 0.4   | v          |

| R <sub>SHUTDOWN</sub> | Shut-down impedance                     | Shut-down Impedance of CHG MOS / DSG<br>MOS / VBUS MOS                                                                                                                                                                            |       |       | 50    | ΚΩ         |

| PARAMETER      |           | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MIN | TYP | MAX | UNIT |

|----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

|                |           | $\label{eq:VDSG} \begin{array}{l} V_{\text{DSG}} \text{ from } 0\% \text{ to } 35\% \ V_{\text{DSG}(\text{ON})(\text{TYP})}, \ V_{\text{BAT}} \ \geq 2.2 \ \text{V}, \\ C_{\text{L}} = 4.7 \ \text{nF} \ \text{between DSG} \ \text{and PACK}, \ 5.1 \text{k}\Omega \\ \text{between DSG} \ \text{and } C_{\text{L}}, \ 10 \ \text{M}\Omega \ \text{between PACK} \\ \text{and DSG} \end{array}$                                                                    |     | 250 | 500 |      |

| t <sub>R</sub> | Rise time | $\label{eq:V_CHG} \begin{array}{l} V_{CHG} \mbox{ from 0\% to 35\% } V_{CHG(ON)(TYP)}, \ V_{BAT} \geq 2.2 \ V, \\ C_L = 4.7 \ nF \ between \ CHG \ and \ BAT, \ 5.1 \ k\Omega \\ between \ CHG \ and \ C_L, \ 10 \ M\Omega \ between \ PACK \\ and \ CHG \end{array}$                                                                                                                                                                                               |     | 250 | 500 | μS   |

|                |           | $\label{eq:VBMC} \begin{array}{l} V_{\text{BMC}} \text{ from } 0\% \text{ to } 35\% \ V_{\text{BMC}(\text{ON})(\text{TYP})}, \ V_{\text{BAT}} \geq 2.2 \ \text{V}, \\ C_{\text{L}} = 4.7 n \text{F} \text{ between } V_{\text{BMC}} \text{ and } V_{\text{BUS}}, \ 5.1 \text{k}\Omega \\ \text{between } V_{\text{BMC}} \text{ and } C_{\text{L}}, \ 10 M\Omega \text{ between } V_{\text{BUS}} \text{ and } \\ V_{\text{BMC}} \end{array}$                         |     | 250 | 500 |      |

|                |           | $\label{eq:VDSG} \begin{array}{l} V_{\text{DSG}} \text{ from } V_{\text{DSG}(\text{ON})(\text{TYP})} \ \text{ to } 1 \ \text{V}, \ \text{V}_{\text{BAT}} \geq 2.2 \ \text{V}, \ \text{C}_{\text{L}} \\ = 4.7 n \text{F} \ \text{between } \text{DSG} \ \text{and } \text{PACK}, \ 5.1 \ \text{k}\Omega \\ \\ \text{between } \text{DSG} \ \text{and } C_{\text{L}}, \ 10 \ \text{M}\Omega \ \ \text{between } \text{PACK} \\ \\ \text{and } \text{DSG} \end{array}$ |     | 120 | 250 | μS   |

|                |           | $ \begin{array}{l} V_{BMC} \mbox{ from } V_{BMC(ON)(TYP)} \mbox{ to 1 } V,  V_{BAT} \geq  2.2  V,  C_L = \\  4.7nF \mbox{ between } V_{BMC} \mbox{ and } V_{BUS},  5.1  k\Omega \mbox{ between } \\  V_{BMC} \mbox{ and } C_L,  10  M\Omega \mbox{ between } V_{BMC} \mbox{ and } V_{BUS} \end{array} $                                                                                                                                                             |     | 120 | 250 | μS   |

|                |           | $\label{eq:V_CHG} \begin{array}{l} V_{CHG} \mbox{ from } V_{CHG(ON)(TYP)} \mbox{ to 1 V, } V_{BAT} \geq 2.2 \mbox{ V, } C_L \\ = 4.7 \mbox{ nF between CHG and BAT, } 5.1 \mbox{ k} \Omega \\ \mbox{ between CHG and } C_L, \mbox{ 10 } M\Omega \mbox{ between PACK} \\ \mbox{ and CHG} \end{array}$                                                                                                                                                                |     | 90  | 150 | μS   |

| tF             | Fall Time | $\label{eq:VDSG} \begin{array}{l} V_{\text{DSG}} \text{ from } V_{\text{DSG(ON)(TYP)}} \text{ to } 1 \text{ V},  V_{\text{BAT}} \geq 2.2 \text{ V},  C_{\text{L}} \\ = & 4.7 \text{ nF} \text{ between DSG and PACK, } 5.1  \Omega \\ \text{between DSG and } C_{\text{L}}, 10  M\Omega \text{ between PACK} \\ \text{and DSG} \end{array}$                                                                                                                         |     | 60  | 100 | μS   |

|                |           | $\label{eq:VBMC} \begin{array}{l} \text{VBMC from VBMC(ON)(TYP) to 1 V, VBAT} \geq \\ 2.2 \text{ V, } C_L = 4.7 n \text{F} \text{ between } V_{\text{BMC}} \text{ and } V_{\text{BUS}}, 5.1 \text{k}\Omega \\ \text{between } V_{\text{BMC}} \text{ and } C_L, 10 M\Omega \text{ between } V_{\text{BUS}} \text{ and} \\ V_{\text{BMC}} \end{array}$                                                                                                                |     | 60  | 100 | μS   |

|                |           | VCHG from VCHG(ON)(TYP) to 1 V, VBAT $\geq$<br>2.2 V, C <sub>L</sub> = 27 nF between CHG and BAT, 250 $\Omega$<br>between CHG and C <sub>L</sub> , 10 M $\Omega$ between BAT and<br>CHG                                                                                                                                                                                                                                                                             |     | 40  | 100 | μS   |

|                                | PARAMETER                                    | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                               | MIN                  | TYP   | MAX                        | UNIT       |

|--------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------|----------------------------|------------|

| PCHG FET D                     | <b>Drive -</b> V <sub>CC</sub> = 4.4V to 26V |                                                                                                                                                                                                                                                                                                                                               |                      |       |                            |            |

| V <sub>(FETON)</sub>           | Output voltage, $P_{CHG}$ on                 | $V_{\text{PCHG}(\text{ON})}$ = $V_{\text{VCC}}$ – $V_{\text{PCHG}},100~\text{K}\Omega$ between $V_{\text{CC}}$ and PCHG                                                                                                                                                                                                                       | 6                    | 7     | 8                          | V          |

| $V_{(FETOFF)}$                 | Output voltage, P <sub>CHG</sub> off         | $V_{\text{PCHG(OFF)}}$ = $V_{\text{VCC}}$ – $V_{\text{PCHG}},$ 100 K $\Omega$ between $V_{\text{CC}}$ and PCHG                                                                                                                                                                                                                                | -0.4                 |       | 0.4                        | V          |

| tr                             | Rise Time                                    | $ \begin{array}{l} V_{\text{PCHG}} \text{ from 10\% to 90\% } V_{\text{PCHG(ON)(TYP)}}, V_{\text{CC}} \geq 8 \text{ V}, \\ C_{\text{L}} = 4.7 \text{ nF between PCHG and } V_{\text{CC}}, 5.1 \text{k}\Omega \\ \text{between PCHG and } C_{\text{L}}, 100 \text{ k}\Omega \text{ between CHG} \\ \text{and } V_{\text{CC}} \end{array} $     |                      | 40    | 200                        | μS         |

| tF                             | Fall Time                                    | $ \begin{array}{l} V_{\text{PCHG}} \text{ from 90\% to 10\% } V_{\text{PCHG(ON)(TYP)}},  V_{\text{CC}} \geq 8  V, \\ C_{\text{L}} = 4.7  \text{nF} \text{ between PCHG and } V_{\text{CC}},  5.1 \text{k}\Omega \\ \text{between PCHG and } C_{\text{L}},  100  \text{k}\Omega \text{ between CHG} \\ \text{and } V_{\text{CC}} \end{array} $ |                      | 40    | 200                        | μS         |

| FUSE Drive                     | $-V_{\rm CC} = 4.4$ V to 26V                 |                                                                                                                                                                                                                                                                                                                                               |                      |       |                            | 4          |

|                                |                                              | VBAT ≥ 8 V, CL = 1 nF, IAFESDSG = 0 µA                                                                                                                                                                                                                                                                                                        | 6                    | 7.5   | 8.65                       | V          |

| V <sub>OH</sub>                | Output voltage high                          | VBAT < 8 V, CL = 1 nF, IAFESDSG = 0 μA                                                                                                                                                                                                                                                                                                        | V <sub>BAT</sub> –0. |       | VBAT                       | V          |

| V <sub>IH</sub>                | Input voltage high                           |                                                                                                                                                                                                                                                                                                                                               | 1.5                  | 2     | 2.5                        | V          |

| I <sub>AFESDSG(PU)</sub>       | Internal pullup current                      | VBAT ≥ 8 V, VAFESDSG = VSS                                                                                                                                                                                                                                                                                                                    |                      | 150   | 330                        | nA         |

| I <sub>DN</sub>                | Internal pullup current                      |                                                                                                                                                                                                                                                                                                                                               | 41                   | 51    | 61                         | kΩ         |

| RAFESDSG                       | Output impedance                             |                                                                                                                                                                                                                                                                                                                                               | 2                    | 2.6   | 3.2                        | kΩ         |

| C <sub>IN</sub>                | Input capacitance                            |                                                                                                                                                                                                                                                                                                                                               |                      | 5     |                            | pF         |

| t <sub>DELAY</sub>             | Fuse trip detection delay                    |                                                                                                                                                                                                                                                                                                                                               | 128                  |       | 256                        | μS         |

| t <sub>RISE</sub>              | Fuse output rise time                        | VBAT ≥ 8 V, CL = 1 nF, VOH = 0 V to 5 V                                                                                                                                                                                                                                                                                                       |                      | 5     | 20                         | μS         |

| Internal Tem                   | perature Sensor - V <sub>CC</sub> = 4.4      | 4V to 26V                                                                                                                                                                                                                                                                                                                                     |                      |       |                            | <u> </u>   |

|                                | Internal temperature                         | V <sub>TEMPP</sub>                                                                                                                                                                                                                                                                                                                            | -1.9                 | -2.0  | -2.1                       | mV/        |

| V <sub>TEMP</sub>              | sensor voltage drift                         | Vtempp - Vtempn                                                                                                                                                                                                                                                                                                                               | 0.177                | 0.178 | 0.179                      | °C         |

| δ°C                            | Accuract of Temp.                            | Single point calibration                                                                                                                                                                                                                                                                                                                      | -3                   |       | 3                          | °C         |

| External Ten                   | nperature Sensor - V <sub>CC</sub> = 4       | 4V to 26V                                                                                                                                                                                                                                                                                                                                     |                      |       |                            |            |

|                                |                                              | TS1, TS2, TS3, TS4, VBIAS = VREF1                                                                                                                                                                                                                                                                                                             | -0.2                 |       | 0.8 ×<br>V <sub>REF1</sub> | V          |

| V <sub>IN</sub>                | Input voltage range                          | TS1, TS2, TS3, TS4, VBIAS = VREG                                                                                                                                                                                                                                                                                                              | -0.2                 |       | 0.8 ×<br>V <sub>REG</sub>  | V          |

| R <sub>NTC(PU)</sub>           | Internal pullup<br>resistance                | TS1, TS2, TS3, TS4                                                                                                                                                                                                                                                                                                                            | 14.4                 | 18    | 21.6                       | kΩ         |

| $R_{\text{NTC}(\text{DRIFT})}$ | Resistance drift Over temperature            | TS1, TS2, TS3, TS4                                                                                                                                                                                                                                                                                                                            | -360                 | -280  | -200                       | PPM/<br>°C |

| Internal 2.0V                  | <b>LDO -</b> $V_{CC} = 4.4V$ to 26V          |                                                                                                                                                                                                                                                                                                                                               |                      |       |                            |            |

| V <sub>REG</sub>               | LDO Regulator voltage                        |                                                                                                                                                                                                                                                                                                                                               | 1.9                  | 2     | 2.1                        | V          |

| $\Delta V_{O(TEMP)}$           | Regulator output over temperature            | $\Delta V_{\text{REG}}/\Delta T_{\text{A}}$ , I <sub>REG</sub> = 10 mA                                                                                                                                                                                                                                                                        |                      | ±0.25 |                            | %          |

| $\Delta V_{O(\text{LINE})}$    | Line regulation                              | $\Delta V_{\text{REG}}/\Delta V_{\text{BAT}}, V_{\text{BAT}}=10 \text{ mA}$                                                                                                                                                                                                                                                                   | -0.6                 |       | 0.5                        | %          |

| $\Delta V_{O(\text{LOAD})}$    | Load regulation                              | $\Delta V_{REG} / \Delta I_{REG}$ , $I_{REG} = 0$ mA to 10 mA                                                                                                                                                                                                                                                                                 | -1.5                 |       | 1.5                        | %          |

|                                 | PARAMETER                                  | TEST CONDITIONS                                                                           | MIN      | TYP     | MAX   | UNIT |

|---------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------|----------|---------|-------|------|

| I <sub>REG</sub>                | Regulator output current limit             | $V_{REG} = 0.9 \times V_{REG(NOM)}, V_{IN} > 4.4V$                                        | 20       |         |       | mA   |

| I <sub>SC</sub>                 | Regulator shortcircuit                     | $V_{\text{REG}} = 0 \times V_{\text{REG(NOM)}}$                                           | 25       | 40      | 55    | mA   |

| PSRR <sub>REG</sub>             | Power supply rejection ratio               | $\Delta V_{BAT}/\Delta V_{REG}$ , I <sub>REG</sub> =10mA ,V <sub>IN</sub> > 2.5V, f =10Hz |          | 40      |       | dB   |

| V <sub>SLEW</sub>               | Slew rate enhancement<br>voltage threshold | V <sub>REG</sub>                                                                          | 1.78     | 1.85    |       | V    |

| Internal 1.5V                   | <b>LDO -</b> $V_{CC} = 4.4V$ to 26V        | I                                                                                         | 1        |         |       |      |

| V <sub>REG15</sub>              | LDO regulator voltage                      |                                                                                           | 1.35     | 1.5     | 1.65  | V    |

| V <sub>PORth</sub>              | POR raise threshold                        | Raise threshold                                                                           | 1.2      |         | 1.45  | V    |

| V <sub>PORhys</sub>             | POR hysteresis Voltage                     | Hysteresis Voltage                                                                        |          | 0.1     |       | V    |

| $\Delta V_{O(TEMP)}$            | Regulator output over temperature          | $\Delta V_{\text{REG}} / \Delta T_{\text{A}}$ , I <sub>REG</sub> = 40 mA                  |          | ±0.25   |       | %    |

| $\Delta V_{O(\text{LINE})}$     | Line regulation                            | $\Delta V_{REG} / \Delta V_{BAT}$ , $V_{BAT}$ = 40 mA                                     | -0.6     |         | 0.5   | %    |

| $\Delta V_{O(\text{LOAD})}$     | Load regulation                            | $\Delta V_{REG} / \Delta I_{REG}$ , $I_{REG} = 0$ mA to 40 mA                             | -1.5     |         | 1.5   | %    |

| I <sub>REG</sub>                | Regulator output current limit             | $V_{REG} = 0.9 \times V_{REG(NOM)}, V_{IN} > 4.4V$                                        | 30       |         |       | mA   |

| Internal 3.3V                   | <b>LDO -</b> V <sub>CC</sub> = 4.4V to 26V |                                                                                           | 1        |         |       |      |

| V <sub>REGRTC</sub>             | 3.3V regulator voltage                     | 3.3V LDO output                                                                           | 3.135    | 3.3     | 3.465 | V    |

| I <sub>LOAD</sub>               | Regulator output current                   |                                                                                           |          | 20      | 30    | V    |

| $\Delta V_{O(TEMP)}$            | Regulator output over temperature          | $\Delta V_{REG} / \Delta T_A$ , I <sub>REG</sub> = 10 mA                                  |          | ±0.25   |       | V    |

| $\Delta V_{O(\text{LINE})}$     | Line regulation                            | $\Delta V_{REG} / \Delta V_{BAT}$ , $V_{BAT}$ =10 mA                                      | -0.6     |         | 0.50  | %    |

| $\Delta V_{O(\text{LOAD})}$     | Load regulation                            | $\Delta V_{REG}/\Delta I_{REG}$ , $I_{REG} = 0$ mA to 10 mA                               | -1.5     |         | 1.50  | %    |

| R <sub>sw</sub>                 | Switch resistance                          |                                                                                           |          | 5       | 6.5   | Ω    |

| I <sub>OCP</sub>                | Over current protection                    |                                                                                           | 50       | 100     | 150   | mA   |

| Low-Frequer                     | ncy Oscillator - V <sub>CC</sub> = 4.4V    | to 26V                                                                                    | •        |         |       |      |

| f <sub>LFO</sub>                | Operating frequency                        |                                                                                           |          | 524.288 |       | kHz  |

|                                 | _                                          | TA = -20°C to 70°C, includes frequency drift                                              | -1.5     | ±0.25   | 1.5   | %    |

| $f_{LFO(ERR)}$                  | Frequency error                            | $T_A = -40^{\circ}C$ to 85°C, includes frequency drift                                    | -2.5     | ±0.25   | 2.5   | %    |