# **AN-PJ1003**

# Understanding PANJIT Medium Voltage and Super Junction MOSFET Datasheet Parameters

To learn more about PANJIT International Inc., please visit our website at <a href="https://www.panjit.com">www.panjit.com</a>

August 2022 Rev.01

## **Table of Contents**

| 1 | Revision History                                  | 2  |

|---|---------------------------------------------------|----|

| 2 | Introduction                                      |    |

| 3 | PANJIT Medium Voltage MOSFET structure and lineup |    |

| 4 | PANJIT Super Junction MOSFET structure and lineup | 4  |

| 5 | Understanding MOSFET Datasheet Parameters         |    |

|   | 5.1 Highlighted feature and introduction          | 6  |

|   | 5.2 Absolute maximum rating                       | 7  |

|   | 5.3 Thermal and electrical characteristics        |    |

|   | 5.4 Characteristic curves                         | 15 |

|   | 5.5 Device characteristic important notice        | 19 |

| 6 | Conclusions                                       | 20 |

| 7 | References                                        | 20 |

## 1 Revision History

| Rev.   | Revision Description   | Edit by           | Date       |

|--------|------------------------|-------------------|------------|

| Rev.00 | Document Release       | Arief Noor Rahman | 2022/07/14 |

| Rev.01 | Rev.01 Products Lineup |                   | 2022/08/26 |

|        |                        |                   |            |

|        |                        |                   |            |

#### 2 Introduction

Power MOSFETs are widely used as switches in various high efficiency power converter applications for its low switching and conduction losses. During design process, engineers use device datasheet provided by manufacturer to understand the device characteristic and make decision of the device suitability for the circuit. Despite of the crucial role of a datasheet, engineers often have misconceptions on datasheet parameters. This application note is aimed to help engineers to understand datasheet parameters, how they were obtained, and how to correlate it to circuit performance.

In PANJIT, we have developed MOSFET technologies for medium voltage (MV-MOSFET) range (60V, 80V, and 100V) and super junction (SJ-MOSFET) range (600V and 650V). In the next sections, we present our MV-MOSFET and SJ-MOSFET lineup followed with the explanation on datasheet parameters and how they were obtained. For some specific parameters with big discrepancy between MV- and SJ-MOSFETs, further explanation is provided.

### 3 PANJIT Medium Voltage MOSFET structure and lineup

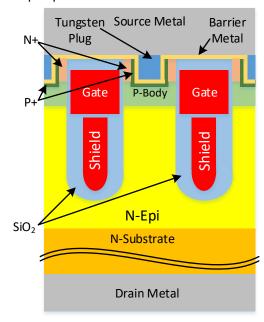

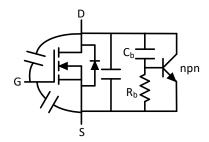

In PANJIT, the MV-MOSFET lineup has been developed using shielded gate trench (SGT) structure as shown in Figure 1. The shield is internally connected to source pin which protecting the gate finger from the drain by reducing the gate to drain capacitance and increasing drain to source capacitance. Resulting in improved gate robustness and lower possibility of false turn-on. Furthermore, the shield is created using polysilicon which have significantly higher resistance than metal that forms a series RC connection between drain to source which behaves as an internal snubber. Where it benefits the device with softer switching characteristic and lower EMI emission. Our current MV-MOSFET lineup is provided in Table 1.

Figure 1. PANJIT MV-MOSFET with shielded gate trench structure

August 2022 Rev.01 3/21

#### Table 1. PANJIT 100V MV-MOSFET lineup

\*in development

|                |        | TO-LL                       | TO-263                      | DFN5060-8L                   | DFN5060S-8L                             | DFN3333S-8L                  | TO-220AB-L                  |

|----------------|--------|-----------------------------|-----------------------------|------------------------------|-----------------------------------------|------------------------------|-----------------------------|

| Voltage<br>(V) | SL/ LL |                             |                             |                              |                                         |                              |                             |

| 100            | SL     | *PSMN015N10NS2<br>(1.5mohm) | *PSMB033N10NS2<br>(3.3mohm) | PSMQC040N10NS2<br>(4.4mohm)  | *PSMQF026N10NS2<br>(2.6mohm)            | *PSMQE085N10NS2<br>(8.5mohm) | *PSMP033N10NS2<br>(3.3mohm) |

| 100            | SL     | *PSMN027N10NS2<br>(2.7mohm) | *PSMB042N10NS2<br>(4.2mohm) | *PSMQC072N10NS2<br>(7.2mohm) | *PSMQF035N10NS2<br>(3.5mohm)            | *PSMQE092N10NS2<br>(9.2mohm) | *PSMP042N10NS2<br>(4.2mohm) |

| 100            | SL     | ,                           | PSMB050N10NS2<br>(5.0mohm)  | *PSMQC089N10NS2<br>(8.9mohm) | , , , , , , , , , , , , , , , , , , , , | ,                            | PSMP050N10NS2<br>(5.0mohm)  |

| 100            | SL     |                             |                             |                              |                                         |                              | *PSMP093N10NS2<br>(9.3mohm) |

|                |        | DFN5060-8L                   | DFN5060S-8L                  | DFN3333-8L<br>(Cu Wire)     | DFN3333S-8L<br>(Cu Clip)     | TO-252AA<br>(DPAK)          |

|----------------|--------|------------------------------|------------------------------|-----------------------------|------------------------------|-----------------------------|

| Voltage<br>(V) | SL/ LL |                              |                              |                             |                              |                             |

| 100            | LL     | *PSMQC038N10LS2<br>(3.8mohm) | *PSMQF025N10LS2<br>(2.5mohm) | *PSMQB230N10LS2<br>(23mohm) | *PSMQE080N10LS2<br>(8.0mohm) | *PSMD081N10LS2<br>(8,1mohm) |

| 100            | LL     | *PSMQC055N10LS2<br>(5,5mohm) | *PSMQF034N10LS2<br>(3.4mohm) | (==:::::::::)               | (5151.1511.11)               | *PSMD093N10LS2<br>(9.3mohm) |

| 100            | LL     | *PSMQC078N10LS2<br>(7.8mohm) | ,                            |                             |                              | *PSMD130N10LS2<br>(13mohm)  |

| 100            | LL     | *PSMQC090N10LS2<br>(9mohm)   |                              |                             |                              | *PSMD240N10LS2<br>(24mohm)  |

| 100            | LL     | *PSMQC120N10LS2<br>(12mohm)  |                              |                             |                              |                             |

| 100            | LL     | *PSMQC240N10LS2<br>(24mohm)  |                              |                             |                              |                             |

#### 4 PANJIT Super Junction MOSFET structure and lineup

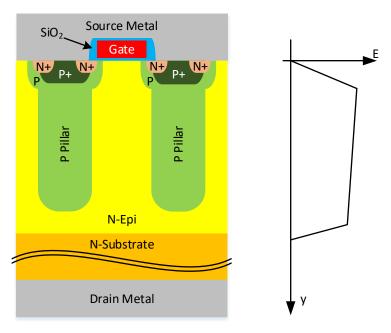

The main design objective for SJ-MOSFET is to achieve low ON resistance and low parasitic capacitance to reduce both conduction and switching losses. The solution is to use a deep-trench structure also known as super-junction structure that is created using P-pillar trench. Figure 2 shows the structure of PANJIT super-junction MOSFET (SJ-MOSFET). Compared to the predecessor design (planar structure), super-junction structure is able to achieve a uniform electric field throughout the epitaxial layers as depicted in Figure 2 (right). Where it allows for higher doping concentration and thinner epitaxial layer. Both, resulting in significantly lower specific ON resistance which allows for smaller die size and consequently lower parasitic capacitance compared to its predecessor. Our current SJ-MOSFET lineup offering 600V-650V voltage rating is presented in Table 2.

August 2022 Rev.01 4/21

Figure 2. PANJIT HV-MOSFET with super-junction structure

TO-247 ITO-220AB-F TO-220AB-L TO-252AA в۷ Rdson TO-263 **Series** (V) (mohm) 74 PJMH074N60FRC 99 PJMH099N60EC PJMF120N60EC PJMP120N60EC PJMH120N60EC 120 190 PJMH190N60E1 PJMF190N60E1 PJMP190N60E1 600 280 PJMF280N60E1 360 PJMF360N60EC PJMP360N60EC PJMD360N60EC 580 PJMF580N60E1 PJMD580N60E1 PJMP900N60EC PJMD900N60EC 900 PJMF900N60EC PJMF130N65EC PJMP130N65EC PJMB130N65EC 130 SJ MOSFET 650V 210 PJMF210N65EC PJMP210N65EC PJMB210N65EC 280 PJMF280N65E1 650 310 PJMF310N65EC PJMP310N65EC PJMB310N65EC 390 PJMF390N65EC PJMP390N65EC PJMD390N65EC PJMB390N65EC PJMD600N65E1 600 PJMF600N65E1 PJMF990N65EC PJMP990N65EC PJMD990N65EC 990

Table 2. PANJIT SJ-MOSFET lineup

## 5 Understanding MOSFET Datasheet Parameters

Datasheet provides information to the engineers about various device parameters and some additional information. However, many of the information are not exactly relevant for switching converter application while some are not very straight-forward to understand. The definition of each parameters and the measurement circuit and method are presented to help the reader to thoroughly understand every parameter.

August 2022 Rev.01 5/21

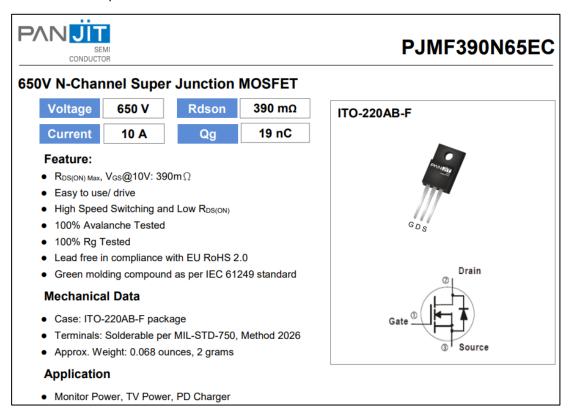

As an example, our PANJIT PJMF390N65EC (650V, 10A, 390 m $\Omega$ ) [1] super-junction high voltage MOSFET is used in this explanation. The explanation of each parameters is explained in the next sub-sections.

#### 5.1 Highlighted feature and introduction

This section shows the highlighted feature of the device, typically the basic such as part number, voltage and current ratings, and resistance rating. Highlighted feature of the device such as a few test items and device compliance are also commonly mentioned in this section. Lastly, the intended market/application and sometimes intended circuit topology are also typically mentioned to help the customer to choose the device.

Figure 2. Datasheet of PJMF390N65EC, highlighted feature and introduction

In PANJIT MOSFET datasheet, we mentioned 100% avalanche tested and 100%  $R_g$  (internal gate resistance) tested on top of the typical test to give more confidence to the engineer about our device reliability/ruggedness performance. The avalanche performance is tested at the manufacturing site for every production device at 50% rated avalanche energy. The  $R_g$  is tested as an indicator of the semiconductor process manufacturing quality (epitaxial, etching, deposition, doping, oxide growing, etc.) and compared with a set toleration limit. Devices that failed on either or both test are screened out from the final product as it is indicated to have defects and will fail prematurely if otherwise assembled into the customer product.

The MOSFET is targeted for market monitor power, TV power and PD charger, which practically is based on ZVS topologies such as LLC or active clamp flyback, and also PFC for application

greater than 75W.

#### 5.2 Absolute maximum rating

Table 3 provides the absolute operating limits of the device and the circuit should be designed to operate the device within the limits for reliable operation. It is important to maintain a reasonable operating margin from the absolute maximum rating to ensure the limits are never violated while operating too close to the maximum rating can resulting in shortened expected lifetime.

Table 3. Absolute maximum ratings of PJMF390N65EC

| PARAMETER                                 | SYMBOL           | LIMIT           | UNITS     |      |  |

|-------------------------------------------|------------------|-----------------|-----------|------|--|

| Drain-Source Voltage @ T <sub>j,max</sub> | V <sub>DS</sub>  | 700             |           |      |  |

| Drain-Source Voltage                      |                  | V <sub>DS</sub> | 650       | V    |  |

| Gate-Source Voltage                       | V <sub>G</sub> s | ±30             |           |      |  |

| Continuous Dunin Coursest                 | Tc = 25°C        | ,               | 10        | А    |  |

| Continuous Drain Current                  | Tc = 100°C       | ID              | 6.2       |      |  |

| Pulsed Drain Current                      | Tc = 25°C        | I <sub>DM</sub> | 22        | Α    |  |

| Single Pulse Avalanche Energy             | •                | Eas             | 220       | mJ   |  |

| MOSFET dv/dt ruggedness                   |                  | dV/dt           | 50        | V/ns |  |

| Barras Biasinatian                        | Tc = 25°C        | Б               | 29.5      | 10/  |  |

| Power Dissipation                         | Tc = 100°C       | P <sub>D</sub>  | 12        | W    |  |

| Insulation Withstand Voltage for ITO-220  | V <sub>ISO</sub> | 3.5             | kV        |      |  |

| Operating Junction and Storage Tempera    | ture Range       | TJ, TSTG        | -55 ~ 150 | °C   |  |

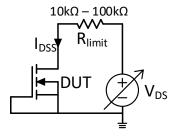

$V_{DS}$  and  $V_{DS}$  (@ $T_{j,max}$ ): the voltage limit that may be applied before the drain source leakage current ( $I_{dss}$ ) exceed a limit threshold ( $100\mu A - 1mA$ ) which resulting in excessive loss. For converter design, it is highly recommended to make sure to keep a reasonable margin for the  $V_{ds}$  spike to this absolute limit.

$V_{GS}$ : voltage is the allowable voltage limit on the gate. The gate structure of a MOSFET is only separated with a very thin oxide (SiO<sub>2</sub>) layer that is prone to failure if excessive voltage is applied.I<sub>D</sub>: Rated drain current is the required drain to source continuous current (pure continuous conduction loss) to increase the  $T_j$  to maximum  $T_j$  when the device is placed on a "infinite heatsink". Infinite heatsink is a heatsink with tightly controlled temperature which is maintained at fixed temperature (25°C and 100°C). It is common for the manufacturer to use theoretical calculation as shown in Equation 1 to obtain this parameter instead of actual measurement result. Specific case for low voltage and medium voltage MOSFET that has >100A current rating, the drain current rating often specified for the MOSFET die capability and the bond wire limit.

$$I_{D} = \sqrt{\frac{T_{j,max} - T_{c}}{R_{ds}(T_{j,max}) . R_{th,jc}}}$$

(1)

$I_{DM}$ : Peak drain current is the maximum allowable short current pulse. When the device is exposed to high current on a short pulse time (Typ.  $\leq 1 ms$ ) the device thermal characteristic is considered to be adiabatic. Where all the power dissipation is used to increase the junction temperature with no heat energy flow out to heatsink or surrounding space. This parameter is also commonly calculated theoretically by solving Equation 2 with  $C_{th}$  defined as MOSFET assembly heat capacity. For some manufacturers,  $I_{DM}$  is defined as a fixed multiply of rated  $I_D$  (Typ. 3x to 4x). Furthermore, another factor such as bond wire limit or drain current cutoff may limit the  $I_{DM}$  capability.

$$C_{\text{th}}.(T_{j,\text{max}} - 25^{\circ}C) = \int_{0}^{t} I_{DM}^{2}.R_{ds}(T_{j}) dt$$

(2)

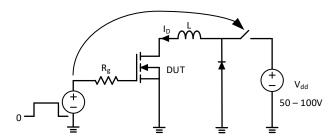

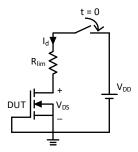

$E_{AS}$ : Maximum allowable single pulse avalanche energy is the maximum energy that can be . Under avalanche, the MOSFET is exposed to  $V_{DS}$  =  $BV_{DSS}$  and high Id simultaneously which resulting in very high power dissipation and fast internal temperature rise. This process occurred in <100 $\mu$ s thus considered to be adiabatic system. Similar to  $I_{DM}$ , this parameter is also strongly related to the device heat capacity. This parameter is obtained using unclamped inductive circuit test as shown in Figure 3.

Figure 3. Measurement circuit for E<sub>AS</sub> characterization

$$E_{AS} = \frac{L \cdot I_D^2}{2} \tag{3}$$

dV/dt: Maximum V<sub>DS</sub> slew rate dV<sub>DS</sub>/dt transient during device turn off switching. A MOSFET exhibit internal RC-npn parasitic structure as shown in Figure 4. When the device is operated with dV<sub>DS</sub>/dt above the limit, the leakage C<sub>b</sub> current will be enough to turn on the npn. Where the npn will be latched ON and causing destructive failure. This phenomenon is more severe on SJ- than on MV- MOSFET due to the higher dV/dt, and used to be a major reliability concern on SJ-MOSFET.

August 2022 Rev.01 8/21

Figure 4. MOSFET internal parasitic npn structure

$P_D$ : is the maximum power dissipation is the required MOSFET power dissipation to increase  $T_j$  to  $T_{j,max}$  with the device attached to infinite heatsink with specified fixed temperature. This parameter often calculated using Equation 4.

$$P_{\rm D} = \frac{T_{\rm j,max} - T_{\rm c}}{R_{\rm th,jc}} \tag{4}$$

$V_{\rm ISO}$ : is the insulating withstanding voltage is the guaranteed package isolation voltage limit based on AC 60Hz test for 1 minutes test duration. This information is only available for MOSFET with isolated TO package.

#### 5.3 Thermal and electrical characteristics

This section provides information regarding the thermal and electrical parameters for a specific test condition. Information presented in this sections is meant to provide some idea on the device characteristic/performance but not on the exact device behavior.

Table 4. Thermal resistance characteristics of PJMF390N65EC

| PARAM              | SYMBOL              | LIMIT           | UNITS |      |

|--------------------|---------------------|-----------------|-------|------|

| Thermal Resistance | Junction-to-Case    |                 | 4.2   | °C/W |

|                    | Junction-to-Ambient | $R_{\theta,ja}$ | 62.5  | C/VV |

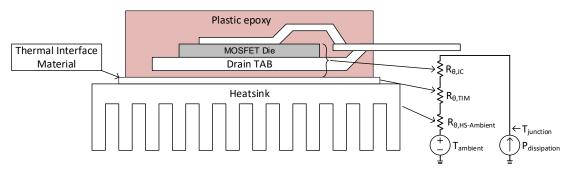

For thermal resistance, two parameters are provided junction-to-case and junction-to-ambient thermal resistance. On the typical application where the MOSFET is attached to a heatsink, R  $\theta$ , jc is used to described the thermal resistance between the junction to the back-side surface of the MOSFET. Together R<sub> $\theta$ ,JC</sub>, R<sub> $\theta$ ,TIM</sub>, and R<sub> $\theta$ ,HS-Ambient</sub> are then combined together to form equivalent thermal circuit as shown in Figure 5 which can be used to model or estimate the junction temperature. When the MOSFET is not attached to a heatsink, R<sub> $\theta$ ,JA</sub> is used for junction temperature estimation.

August 2022 Rev.01 9/21

Figure 5. MOSFET thermal stackup with heatsink attached

The electrical parameters of the MOSFET are typically categorized into three groups. First, static parameters provide information regarding device characteristics with all  $V_{DS}$ ,  $I_{D}$ , and  $V_{GS}$  are constant during the test. Second, dynamic parameters provide information regarding device characteristics during switching transition. Third, body diode parameters, provide the information on the forward voltage and reverse recovery characteristics of the device. Those three parameters were obtained at  $T_j = 25^{\circ}\text{C}$  unless stated otherwise.

| 74270 07 04440 070047047 0744400070400 07 7 0744 00070020 |                     |                                                          |      |      |      |       |  |

|-----------------------------------------------------------|---------------------|----------------------------------------------------------|------|------|------|-------|--|

| PARAMETER                                                 | SYMBOL              | TEST CONDITION                                           | MIN. | TYP. | MAX  | UNITS |  |

| Static                                                    |                     |                                                          |      |      |      |       |  |

| Drain-Source Breakdown Voltage                            | BV <sub>DSS</sub>   | V <sub>GS</sub> =0V, I <sub>D</sub> =250uA               | 650  | 730  | -    | V     |  |

| Gate Threshold Voltage                                    | $V_{GS(th)}$        | V <sub>DS</sub> =V <sub>GS</sub> , I <sub>D</sub> =250uA | 2    | 3    | 4    | V     |  |

| Drain-Source On-State Resistance                          | R <sub>DS(on)</sub> | V <sub>GS</sub> =10V, I <sub>D</sub> =5.0A               | -    | 340  | 390  | mΩ    |  |

| Zero Gate Voltage Drain Current                           | I <sub>DSS</sub>    | V <sub>DS</sub> =650V, V <sub>GS</sub> =0V               | -    | -    | 1    | uA    |  |

| Gate-Source Leakage Current                               | I <sub>GSS</sub>    | $V_{GS}=\pm30V,\ V_{DS}=0V$                              | -    | -    | ±100 | nA    |  |

| Transfer Characteristics                                  | gfs                 | V <sub>DS</sub> =20V, I <sub>D</sub> =11A                | -    | 10   | -    | S     |  |

Table 5. Static electrical characteristics of PJMF390N65EC

$BV_{DSS}$ : is the measured  $V_{DS}$  when the leakage current reaching to a specified threshold (250 $\mu$ A – 1mA) with gate shorted to source.

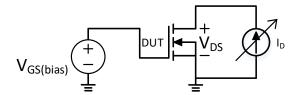

Figure 6. BVDSS and IDSS measurement circuit

August 2022 Rev.01 10/21

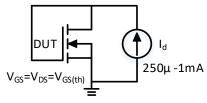

$V_{GS(th)}$ : is the measured gate voltage when the current starts to flow from drain to source. This parameter is measured shorting the drain and gate pin then applying a small current (250 $\mu$ A – 1mA) from drain pin to source pin.

Figure 7. Gate threshold voltage measurement circuit

$R_{DS(on)}$ : is the measured drain to source resistance at the specified gate-source bias voltage and drain-source current. The specified drain-source current is only applied to the DUT for a very short duration (100  $\mu s - 500 \ \mu s$ ) to limit the self-heating effect raise the  $T_j$  during the measurement duration.

Figure 8. ON resistance measurement circuit

$I_{DSS}$ : is the measured drain to source leakage current at the specified rated device  $V_{DS}$  voltage. This parameter is obtained using the circuit shown in Figure 6 with  $V_{DS}$  is set at the voltage device rating.

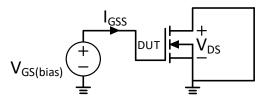

$I_{\text{GSS}}$ : is the measured gate leakage current at the specified maximum positive and negative gate voltage bias.

Figure 9. Gate leakage current measurement circuit

gfs: is the MOSFET transconductance which is defined as the slope/ratio between  $V_{GS}/I_D$  at the specified  $I_D$  with the MOSFET drain-source biased with a constant voltage. The gfs is also shown in the  $V_{GS}$ -  $I_D$  curve (Section 5.4, Figure 18(b)).

Table 6. Dynamic electrical characteristics of PJMF390N65EC

| PARAMETER          | SYMBOL   | TEST CONDITION                                                      | MIN. | TYP. | MAX | UNITS |

|--------------------|----------|---------------------------------------------------------------------|------|------|-----|-------|

| Dynamic            |          |                                                                     |      |      |     |       |

| Total Gate Charge  | Qg       |                                                                     | -    | 19   | -   |       |

| Gate-Source Charge | $Q_{gs}$ | V <sub>DS</sub> =520V, I <sub>D</sub> =11A,<br>V <sub>GS</sub> =10V | -    | 4    | -   | nC    |

| Gate-Drain Charge  | $Q_{gd}$ | VGS=10V                                                             | -    | 8    | -   |       |

August 2022 Rev.01 11/21

| Input Capacitance            | Ciss                | V 400V V 0V                                             | - | 726 | - |    |

|------------------------------|---------------------|---------------------------------------------------------|---|-----|---|----|

| Output Capacitance           | Coss                | V <sub>DS</sub> =400V, V <sub>GS</sub> =0V,<br>f=250kHz | - | 29  | - |    |

| Reverse Transfer Capacitance | Crss                | I=250KHZ                                                | - | 8   |   | pF |

| Effective Output Capacitance | Carra               | V <sub>DS</sub> =0V to 400V,                            |   | 37  |   |    |

| Energy Related               | C <sub>O(er)</sub>  | V <sub>GS</sub> =0V, f=250kHz                           | - | 31  | - |    |

| Turn-On Delay Time           | t <sub>d(on)</sub>  |                                                         | - | 30  | - |    |

| Turn-On Rise Time            | t <sub>r(on)</sub>  | V <sub>DD</sub> =325V, I <sub>D</sub> =11A,             | - | 50  |   | 20 |

| Turn-Off Delay Time          | t <sub>d(off)</sub> | $V_{GS}=10V,R_g=25\Omega$                               | - | 87  | - | ns |

| Turn-Off Fall Time           | t <sub>f</sub>      |                                                         | - | 42  | - |    |

| Gate Resistance              | Rg                  | f=1 MHz                                                 | - | 6.8 | - | Ω  |

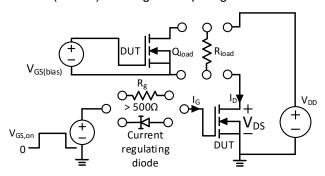

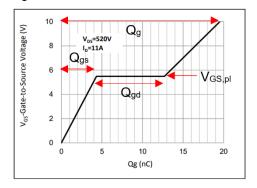

$Q_g$ ,  $Q_{gs}$ , and  $Q_{gd}$ : are the gate charge characteristic of the MOSFET.  $Q_{gs}$  is defined as the required charge needed to raise the gate voltage from the OFF-state up to the plateau voltage ( $V_{gs,pl}$ ). The  $Q_{gd}$  is is defined as the required charge needed to fully discharge the  $V_{Ds}$ . The  $Q_g$  is defined as the required charge needed to raise the gate voltage from OFF-state to VGS-ON under hard-switching condition. Measurement for gate charge is conducted using the circuit shown in Figure 10 with the specified  $V_{DD}$  supply voltage and  $R_{load}$  to reach the specified ON current. The gate charge of the DUT is measured by charging the gate/turning on the MOSFET with very low current source (< 5mA) or using totem-pole gate driver with large gate resistance.

Figure 10. Gate charge measurement circuit

$$Q_{g} = \int_{0}^{\tau} I_{G} dt$$

(5)

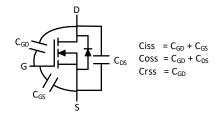

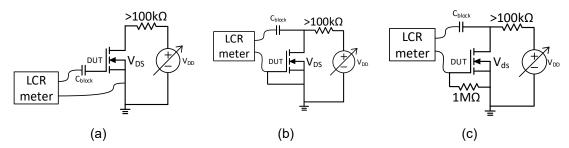

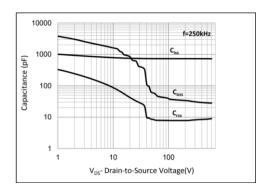

Ciss, Coss, and Crss: are the input, output, and reverse parasitic capacitance of the MOSFFET as described by Figure 11. The MOSFET parasitic capacitance is highly nonlinear since the capacitance is formed by non-linear depletion region which is related to the applied reverse bias voltage. Figure 12 shows the measurement circuit used to obtained the parasitic capacitance and also applying V<sub>DS</sub> bias voltage.

August 2022 Rev.01 12/21

Figure 11. Correlation of different parasitic capacitances

Figure 12. Parasitic capacitance measurement circuit: (a) Ciss, (b) Coss, and (c) Crss

$C_{O(er)}$  and  $C_{O(tr)}$ : First is the effective output capacitance – energy related which is equivalent linear capacitor value that holds same amount of energy as the MOSFET DUT at a specific  $V_{DS}$  voltage. Second is the effective output capacitance – time related which is the equivalent linear capacitor value that holds the same amount of charge as the MOSFET DUT at a specific  $V_{DS}$  voltage. The  $C_{O(er)}$  is related to capacitive energy loss especially during hard-switching operation. The  $C_{O(tr)}$  is related to the time required to discharge the output capacitance, mostly used for calculating the required dead-time in ZVS converter. Both parameters can be obtained by using a series RC circuit with the C formed by MOSFET Coss, as depicted in Figure 13, then Equations 6 and 7 is used to calculate the parameters result. Meanwhile, Equations 8 and 9 are used by some device manufacturers to calculate the  $C_{O(er)}$  and  $C_{O(tr)}$  from Coss measurement curves as depicted in Figure 20.

Figure 13. C<sub>O(er)</sub> and C<sub>O(tr)</sub> experimental measurement circuit

$$C_{O(er)}(V) = \frac{2}{V^2} \int_{0}^{t(V)} V_{DS} I_D dt$$

(6)

$$C_{O(tr)}(V) = \frac{1}{t(V).R_{lim}} ln \left(1 - \frac{V}{V_{DD}}\right)$$

(7)

August 2022 Rev.01 13/21

$$C_{O(er)}(V) = \frac{2}{V^2} \int_{0}^{t(V)} C_{OSS}(V).V dV$$

(8)

$$C_{O(tr)}(V) = \frac{Q_{OSS}(V)}{V} = \frac{1}{V} \int_{0}^{V} C_{OSS}(V) dV$$

(9)

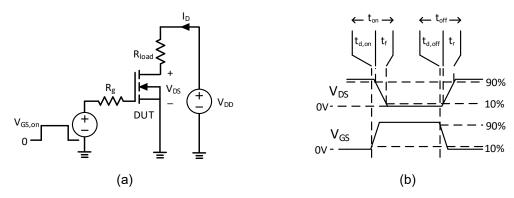

td(on), tr, td(off), and tf: are the delay and transient time during turn on and turn off switching test with specific  $R_{load}$ ,  $V_{DD}$ , and  $R_g$ , and  $V_{GS,on}$ . The test circuit and measurement definition of these parameters are shown in Figure 14.

Figure 14. Switching delay and transient, (a) measurement circuit and (b) waveform definition

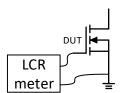

$R_g$ : is the measured equivalent series resistance of the MOSFET obtained using LCR meter. The measurement circuit is shown in Figure 15 and the  $R_g$  is measured at the specified frequency and  $V_{GS}$  bias (Typically  $V_{GS}$  = 0V if not specified).

Figure 15. Internal gate resistance measurement

Table 7. Body diode characteristics of PJMF390N65EC

| PARAMETER                    | SYMBOL          | TEST CONDITION                             | MIN. | TYP. | MAX | UNITS |  |  |

|------------------------------|-----------------|--------------------------------------------|------|------|-----|-------|--|--|

| Drain-Source Diode           |                 |                                            |      |      |     |       |  |  |

| Maximum Continuous Drain-    | la.             |                                            |      |      | 10  | А     |  |  |

| Source Diode Forward Current | Is              | -                                          | -    | -    | 10  | A     |  |  |

| Diode Forward Voltage        | V <sub>SD</sub> | I <sub>S</sub> = 10A, V <sub>GS</sub> = 0V | -    | 0.89 | 1.5 | V     |  |  |

| Reverse Recovery Charge      | Qrr             | Is = 11A,                                  | -    | 3.3  | -   | μC    |  |  |

| Reverse Recovery Time        | Trr             | dI/dt = 100A/µs                            | -    | 291  | -   | ns    |  |  |

August 2022 Rev.01 14/21

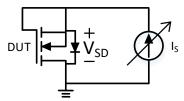

Is: The maximum continuous diode forward current typically is specified at the same device current rating.

$V_{SD}$ : is the forward voltage of the MOSFET body diode measured at the specified forward current. Typical range for  $V_{SD}$  is 0.6 to 1 V.

Figure 16. Body diode forward voltage measurement circuit

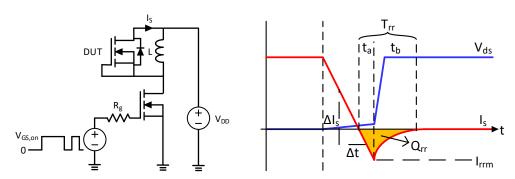

Q<sub>rr</sub> and T<sub>rr</sub>: are the reverse recovery charge and time during hard commutation at the specified diode turn off current slew rate (dl/dt). Slew rate is defined between 50% of forward conduction current and 50% of I<sub>rrm</sub> (maximum reverse recovery current). Figure 17 shows the measurement circuit for reverse-recovery characteristics and the expected ideal waveform. This parameter is very important when the application requires body diode commutation (e.g. synchronous buck or motor inverter) as well as ZVS converter when body diode commutation may occur when the converter operates at light load or experiencing large transient. The reverse-recovery characteristic of MV and SJ MOSFET is differs significantly, and will be discussed further at the section 6.

Figure 17. Body diode reverse recovery, (left) measurement circuit and (b) expected ideal waveform.

#### 5.4 Characteristic curves

Further detail of MOSFET characteristics are provided in the form of characteristic curves to provide the correlation between two measurement parameters.

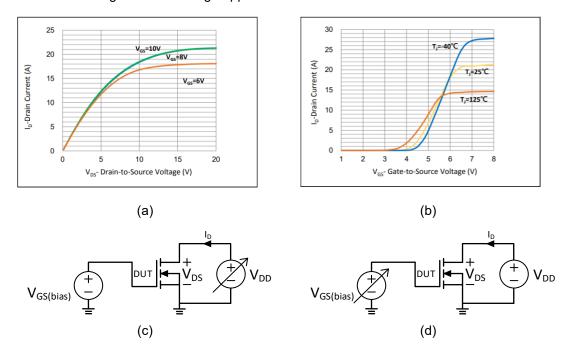

Figure 18 shows the linear characteristic of the MOSFET. First Figure 18(a),  $V_{DS}$  -  $I_{D}$ , is measured at specified  $V_{GS}$  bias. This curves indicates the MOSFET resistive and cut-off behaviors. Second Figure 18(a),  $V_{GS}$  -  $I_{D}$  is measured at the specified  $V_{DS}$  bias. This curves may indicate the effectiveness of  $R_{g}$  variation to tune the switching behavior, with steeper curves (higher gfs) resulting in  $R_{g}$  variation to be less effective. Additionally, it may indicate the

August 2022 Rev.01 15/21

MOSFET performance for linear application. Nevertheless, unless the MOSFET is designed/optimized for linear application, typical power MOSFET has small die size and thus has very weak performance in linear application. These linear characteristics are typically not used for switching converter design/applications.

Figure 18. Linear characteristic curves, (a) $V_{DS}$  -  $I_D$  and (b) $V_{GS}$  -  $I_D$  and its respective measurement circuit (c) and (d)

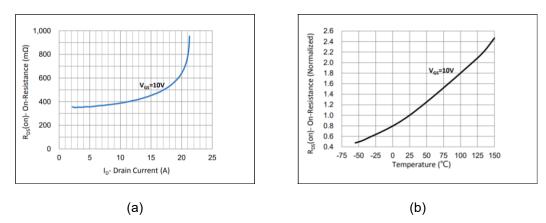

Figure 19 (a) shows  $I_D$  -  $R_{DS(on)}$  relationship at fix specified  $V_{GS}$  bias. At the large drain current beyond the MOSFET rated current, the MOSFET exhibit cut-off behavior where the resistance increases exponentially. MOSFET resistance also increases proportionally with the junction temperature as depicted in Figure 19(b). Both parameters are measured using circuit shown in Figure 8.

Figure 19. ON resistance characteristic (a) RDS(on) - ID and (b) Temp - RDS(on)

Figure 20 shows the relationship between parasitic capacitances (Ciss, Coss, Crss) to V<sub>DS</sub> bias. In a MOSFET, as the parasitic capacitance are formed by both physical dielectric (oxide layer) and depletion layer on the pn-junction. Resulting in significant drop in the capacitance at higher voltage especially for Coss and Crss. These capacitances are measured using circuit shown in Figure 12 at the specified excitation frequency.

Figure 20. Parasitic capacitance curves to  $V_{DS}$  bias characteristic curves

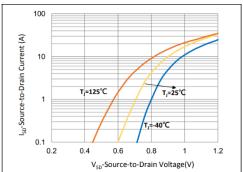

Figure 21 shows the relationship between MOSFET body diode forward current and its forward voltage drop. The body diode has negative temperature coefficient. It is measured using circuit shown in Figure 16.

Figure 21. Body diode forward voltage drop,  $V_{SD} - I_{SD}$

Figure 22 shows the gate charge characteristic which is measured using the circuit depicted in Figure 10. Gate plateau voltage is also shown at around 5.3V.

Figure 22. Gate charge characteristic curve

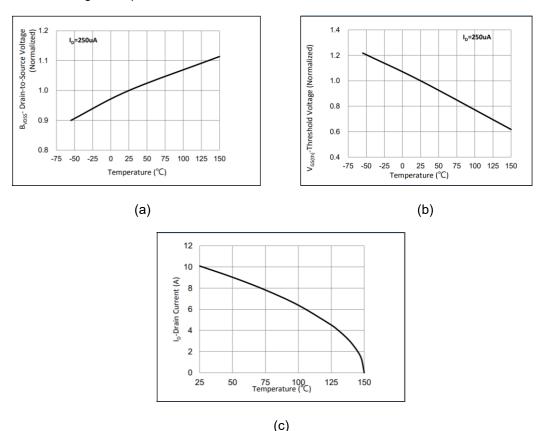

Figure 22 shows the temperature dependent characteristics of the breakdown voltage, gate threshold and continuous current rating. The measurement result was obtained using circuit

provided in Figures 6 and 7 for the first two parameters. The continuous current rating may be obtained using the Equation 1.

Figure 22. Temperature dependent parameters, (a) breakdown voltage, (b) gate threshold voltage, and (c) continuous current rating

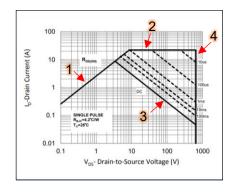

Safe operating area is the safe operating limit of the device that is determined by the current pulse width, (1) resistive limit, (2) pulsed drain current limit, (3) pulse power limit, and (4) breakdown voltage limit. SOA is mostly useful for linear application, which is important for linear efuse, hot-swap, and load switch applications. Nevertheless, it does not have much use for switching application as the device is exposed to both high voltage and current for <500 ns.

Figure 23. Safe operation area

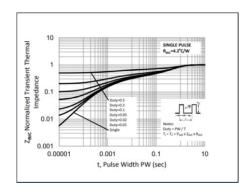

Normalized transient thermal impedance is measured by applying pulsed power dissipation on

the DUT with varying duty cycle. The resulting characteristic curve is used to create the equivalent RC Cauer or Foster network to create the impedance model of the device.

Figure 24. Normalized transient thermal impedance curves

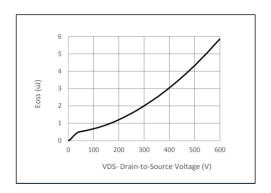

The stored output capacitance energy is shown in Figure 25 for different V<sub>DS</sub> bias voltage. This curve is used to calculate the total output capacitance loss on a hard switching converter.

Figure 25. Stored output capacitance energy

#### 5.5 Device characteristic important notice

Structurally, MOSFET with different voltage rating class, such as low, medium, and high voltage are designed with different structure. Where the goal is to optimized the performance based on the switching characteristics, intrinsic capacitances, and ON resistance. For example, low voltage MOSFET tends to have very low ON resistance down to  $1m\Omega$  range and used with switching frequency over 500 kHz. In such design the design goal is to minimize the gate charge and minimize the ON resistance. Another example, for high voltage MOSFET, the goal is to achieve high voltage breakdown without sacrificing the ON resistance and also achieving dV/dt ruggedness.

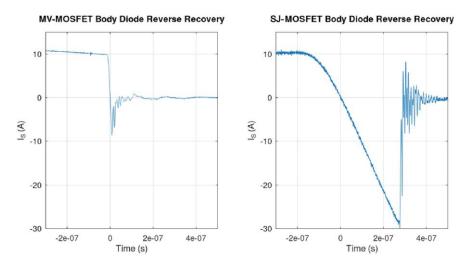

Nevertheless, from the electrical characteristic towards the switching converter operation generally the difference between these MOSFETs are not too significant. Except, body diode reverse recovery performance especially for high voltage super junction MOSFET structure. As mentioned earlier, the super junction is popular for high efficiency switching converter thanks to its low R<sub>DS(on)</sub>. However, the super junction structure has a main downside of creating very large pn-junction for reverse current flow (body diode). Such large pn-junction resulting in large minority carrier (hole) flow during body-diode conduction that needs to recombine during hard commutation. Where, it is resulting in large peak reverse recovery current (I<sub>rrm</sub>) and "snappy" characteristic of SJ-MOSFET body diode. Figure 26 shows the measured reverse recovery waveform of MV- and

August 2022 Rev.01 19/21

SJ- MOSFETs with current slew-rate during commutation at 980A/µs and 100A/µs respectively. Despite of a ten-times higher the slew-rate, the current waveform of MV-MOSFET has much better reverse recovery behavior: (1) significantly lower I<sub>rrm</sub>, Q<sub>rr</sub>, and T<sub>rr</sub>, (2) better softness factor (t<sub>b</sub>/t<sub>a</sub>), and (3) clean recovery behavior without oscillation. Meanwhile, the SJ-MOSFET reverse recovery is significantly poorer at all aspect. The oscillation reverse recovery behavior is practically larger on a converter circuit where the slew rate is easily greater than 400 A/µs.

Figure 26. Body diode reverse recovery waveform of MV- and SJ-MOSFETs

Such characteristic is the reason why circuit that requires constant body diode commutation (such as synchronous buck or inverter) are completely avoided for SJ-MOSFET application. And only use the SJ-MOSFET for application where body diode commutation is not possible by design (e.g. boost PFC) or where body diode commutation occurs only for short duration and at a certain condition (for example on a ZVS converter such as LLC or phase shift full bridge during light load, soft-start, or large load transient). Careful design is required to ensure dl/dt during body diode commutation and the duration of hard commutation is short as possible.

#### 6 Conclusions

The MOSFET datasheet parameters has been explained in detail. The definition of the parameters, the measurement circuit, and its use for circuit design has been presented.

Nevertheless, different manufacturer has their own different definition, measurement circuit, calculation method, limit/criteria for their datasheet. Thus this application note should only be used as a general information to help understand the device characteristic.

#### 7 References

[1] PANJIT International Inc., "PJMF390N65EC - Datasheet," October 2021.

August 2022 Rev.01 20/21

#### **DISCLAIMER**

PANJIT International Inc. Reserves the right to make changes, corrections, enhancements, modifications, and improvements to PANJIT products and/or to this document without further notice. The recipient of this document must verify any function described herein in the real application. PANJIT assumes no liability for customers' product design or applications.

Products are not authorized for use as critical components in life support devices/systems, devices/systems requiring extraordinarily high level quality and/or reliability and/or a malfunction/failure may cause loss of human life, serious public impact. PANJIT assumes no liability for product if use in these situations.

#### COMMENTS

Your feedback will help us to continuously improve the quality of this document. Any information that you feel wrong or unclear, please send your proposal to: <a href="mailto:sales@panjit.com.tw">sales@panjit.com.tw</a>